- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370792 > HYB39S16320TQ-8 (SIEMENS A G) 128 x 64 pixel format, LED Backlight available PDF資料下載

參數(shù)資料

| 型號(hào): | HYB39S16320TQ-8 |

| 廠商: | SIEMENS A G |

| 元件分類(lèi): | DRAM |

| 英文描述: | 128 x 64 pixel format, LED Backlight available |

| 中文描述: | 512K X 32 SYNCHRONOUS GRAPHICS RAM, 6 ns, PQFP100 |

| 封裝: | TQFP-100 |

| 文件頁(yè)數(shù): | 21/70頁(yè) |

| 文件大?。?/td> | 563K |

| 代理商: | HYB39S16320TQ-8 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)當(dāng)前第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)

HYB 39S16320TQ-6/-7/-8

Semiconductor Group

21

1998-10-01

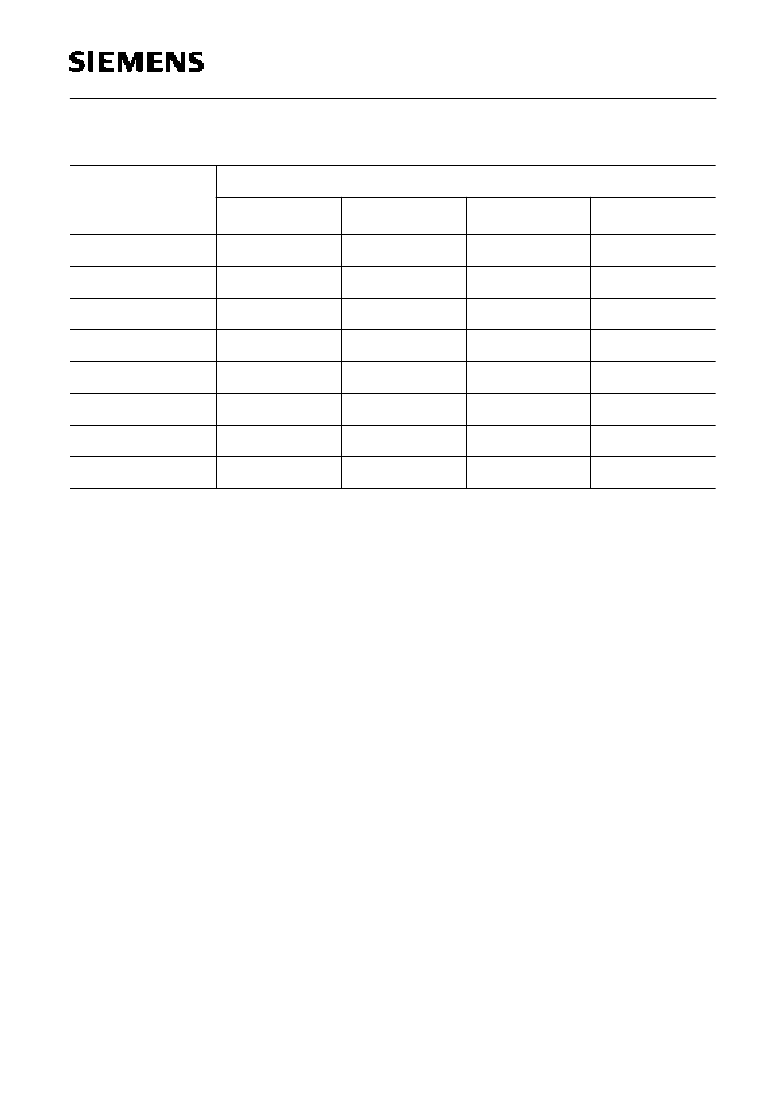

The table shows the masking of data caused by the registered value on the DQ pins, when data is

transfered from Color Register to the 8 succeeding memory locations addressed in the Write Block

command.

When a “1” is registered, the Color Register data will be written to the corresponding DRAM cells,

subject to the DQM and the WPB masking. The overall Block Write mask consists of a combination

of the DQM signals, the WPB mask register and the column/byte mask information.

Block Write Timing Considerations

A Block Write access requires a time period of

t

BWC

to execute, so in general, the cycle after the

Block Write command should be a NOP. However, Active or Precharge commands to the other

bank are allowed. When following a Block Write with a Precharge command to the same bank,

t

BPL

must be met.

Bit Mask mapping of DQ bits

Address

within Written

Block

Byte within Data Word

Byte 3

Byte 2

Byte 1

Byte 0

0

DQ24

DQ16

DQ8

DQ0

1

DQ25

DQ17

DQ9

DQ1

2

DQ26

DQ18

DQ10

DQ2

3

DQ27

DQ19

DQ11

DQ3

4

DQ28

DQ20

DQ12

DQ4

5

DQ29

DQ21

DQ13

DQ5

6

DQ30

DQ22

DQ14

DQ6

7

DQ31

DQ23

DQ15

DQ7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYB39S13620TQ- | 128 x 64 pixel format, LED Backlight available |

| HYB39S16320TQ-10 | 128 x 64 pixel format, LED Backlight available |

| HYB39S16400-1 | 16 MBit Synchronous DRAM |

| HYB39S16400CT-8 | 16 MBit Synchronous DRAM |

| HYB39S16800CT-8 | 16 MBit Synchronous DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB39S1632TQ55 | 制造商:N/A 功能描述:NEW |

| HYB39S16400 | 制造商:INFINEON 制造商全稱(chēng):Infineon Technologies AG 功能描述:16 MBit Synchronous DRAM |

| HYB39S16400-1 | 制造商:INFINEON 制造商全稱(chēng):Infineon Technologies AG 功能描述:16 MBit Synchronous DRAM |

| HYB39S16400AT-10 | 制造商:INFINEON 制造商全稱(chēng):Infineon Technologies AG 功能描述:16 MBit Synchronous DRAM |

| HYB39S16400AT-8 | 制造商:INFINEON 制造商全稱(chēng):Infineon Technologies AG 功能描述:16 MBit Synchronous DRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。