- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385408 > HT95C200 (Holtek Semiconductor Inc.) 8-Bit CID Type Phone Controller MCU PDF資料下載

參數(shù)資料

| 型號: | HT95C200 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | 8-Bit CID Type Phone Controller MCU |

| 中文描述: | 8位偵緝型電話MCU控制器 |

| 文件頁數(shù): | 19/50頁 |

| 文件大小: | 324K |

| 代理商: | HT95C200 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

HT95C200/20P/300/30P

Rev. 0.10

19

October 1, 2002

Preliminary

Timer/Event Counter

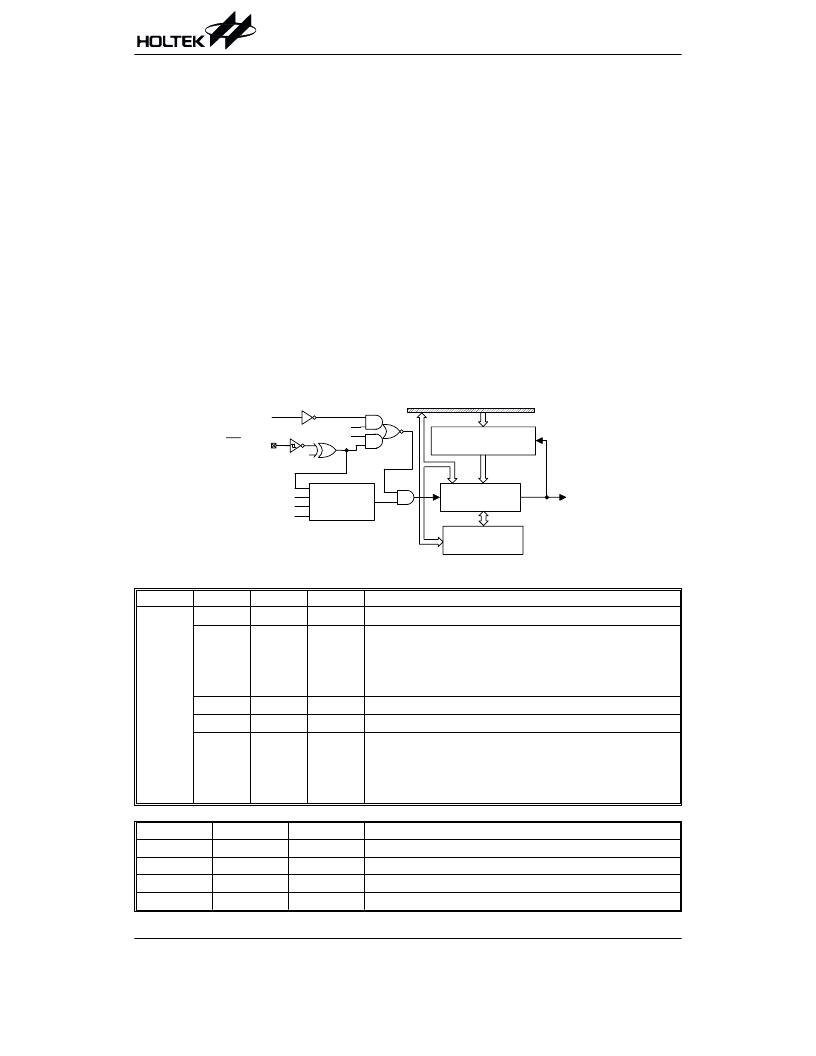

Two timer/event counters (TMR0, TMR1) are imple-

mented in the telephone controller series. The

Timer/Event Counter 0 and Timer/Event Counter 1 con-

tain 16-bits programmable count-up counter and the

clock may come from an external source or internal

source. For TMR0 internal source is instruction clock

(systemclock/4).ForTMR1internalsourceis32768Hz.

Using the 32768Hz clock or instruction clock, there is

only one reference time-base. The external clock input

allows the user to count external events, measure time

intervals or pulse width, or generate an accurate time

base.

There are 3 registers related to Timer/Event Counter 0;

TMR0H, TMR0L, TMR0C. Writing TMR0L only writes

the data into a low byte buffer, but writing TMR0H simul-

taneously writes the data along with the contents of the

low byte buffer into the Timer/Event Counter 0 preload

register (16-bit). The Timer/Event Counter 0 preload

register is changed by writing TMR0H operations. Writ-

ing TMR0L will keep the Timer/Event Counter 0 preload

register unchanged.

Reading TMR0H latches the TMR0L into the low byte

buffer to avoid a false timing problem. Reading TMR0L

returns the contents of the low byte buffer. In other

words, the low byte of the Timer/Event Counter 0 can

not be read directly. It must read the TMR0H first to

make the low byte contents of Timer/Event Counter 0 be

latched into the buffer.

There are 3 registers related to the Timer/Event Counter

1; TMR1H, TMR1L, TMR1C. The Timer/Event Counter

1 operates in the same manner as the Timer/Event

Counter 0.

The TMR0C is the Timer/Event Counter 0 control regis-

ter, which defines the Timer/Event Counter 0 options.

The Timer/Event Counter 1 has the same options as the

Timer/Event Counter 0 and is defined by TMR1C. The

timer/event counter control registers define the operat-

ing mode, counting enable or disable and active edge.

'

(

'

;

'

8

" 7

"

8

( ; #

"

" ' (

8

"

( #

" ' (

" :

8

#

! 8 3

"

" ' ) "

" 8

9 " ,

" 8

9 ( * /

" ) " & 0 2 . + 5 6

3 " :

" :

! !

Timer/Event Counter 0/1

Register

Label

Bits

R/W

Function

TMR0C

(0EH)

TMR1C

(11H)

0~2

RO

Unused bit, read as 0

TE

3

RW

To define the TMR0/TMR1 active edge of timer

For event count or Timer mode

(0=active on low to high; 1=active on high to low)

For pulse width measurement mode

(0=measures low pulse width; 1=measures high pulse width)

TON

4

RW

To enable/disable timer counting (0=disabled; 1=enabled)

5

RO

Unused bit, read as 0

TM0

TM1

6

7

RW

To define the operating mode

Bit 7, 6=01, Event count mode (external clock)

Bit 7, 6=10, Timer mode

Bit 7, 6=11, Pulse width measurement mode

Bit 7, 6=00, Unused

Register

Bits

R/W

Function

TMR0H (0CH)

0~7

RW

Timer/Event Counter 0 higher-order byte register

TMR0L (0DH)

0~7

RW

Timer/Event Counter 0 lower-order byte register

TMR1H (0FH)

0~7

RW

Timer/Event Counter 1 higher-order byte register

TMR1L (10H)

0~7

RW

Timer/Event Counter 1 lower-order byte register

相關PDF資料 |

PDF描述 |

|---|---|

| HT95CXXX | CID Type Phone 8-Bit MCU |

| HT95L400-128QFP-A | LCD Type Phone 8-Bit MCU |

| HT95L100-64QEP-A | LCD Type Phone 8-Bit MCU |

| HT95L10P-64QEP-A | LCD Type Phone 8-Bit MCU |

| HT95L100-64QFP-A | 8-Bit LCD Type Phone Controller MCU |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HT95C20P | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:8-Bit CID Type Phone Controller MCU |

| HT95C300 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:CID Type Phone 8-Bit MCU |

| HT95C30P | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:CID Type Phone 8-Bit MCU |

| HT95C400 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:CID Type Phone 8-Bit MCU |

| HT95C40P | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:LCD Type Phone 8-Bit MCU |

發(fā)布緊急采購,3分鐘左右您將得到回復。