- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄385399 > HT46C65-56 (Holtek Semiconductor Inc.) A/D with LCD Type 8-Bit MCU PDF資料下載

參數(shù)資料

| 型號(hào): | HT46C65-56 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | A/D with LCD Type 8-Bit MCU |

| 中文描述: | 在A / D液晶型8位微控制器 |

| 文件頁(yè)數(shù): | 11/48頁(yè) |

| 文件大?。?/td> | 409K |

| 代理商: | HT46C65-56 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)

HT46R65/HT46C65

Rev. 1.80

11

July 14, 2005

Interrupts

The device provides two external interrupts, two internal

timer/event counter interrupts, an internal time base in-

terrupt, and an internal real time clock interrupt. The in-

terrupt control register 0 (INTC0;0BH) and interrupt

control register 1 (INTC1;1EH) both contain the interrupt

controlbitsthatareusedtosettheenable/disablestatus

and interrupt request flags.

Once an interrupt subroutine is serviced, other inter-

rupts are all blocked (by clearing the EMI bit). This

scheme may prevent any further interrupt nesting. Other

interrupt requests may take place during this interval,

but only the interrupt request flag will be recorded. If a

certain interrupt requires servicing within the service

routine, the EMI bit and the corresponding bit of the

INTC0 or of INTC1 may be set in order to allow interrupt

nesting. Once the stack is full, the interrupt request will

not be acknowledged, even if the related interrupt is en-

abled, until the SP is decremented. If immediate service

is desired, the stack should be prevented from becom-

ing full.

All these interrupts can support a wake-up function. As

an interrupt is serviced, a control transfer occurs by

pushing the contents of the program counter onto the

stack followed by a branch to a subroutine at the speci-

fied location in the ROM. Only the contents of the pro-

gram counter is pushed onto the stack. If the contents of

the register or of the status register (STATUS) is altered

by the interrupt service program which corrupts the de-

sired control sequence, the contents should be saved in

advance.

External interrupts are triggered by a an edge transition

of INT0 or INT1 (ROM code option: high to low, low to

high, low to high or high to low), and the related interrupt

request flag (EIF0; bit 4 of INTC0, EIF1; bit 5 of INTC0)

is set as well. After the interrupt is enabled, the stack is

not full, and the external interrupt is active, a subroutine

call to location 04H or 08H occurs. The interrupt request

flag(EIF0orEIF1)andEMIbitsareallclearedtodisable

other maskable interrupts.

The internal Timer/Event Counter 0 interrupt is initial-

ized by setting the Timer/Event Counter 0 interrupt re-

quest flag (T0F; bit 6 of INTC0), which is normally

caused by a timer overflow. After the interrupt is en-

abled, and the stack is not full, and the T0F bit is set, a

subroutinecalltolocation0CHoccurs.Therelatedinter-

rupt request flag (T0F) is reset, and the EMI bit is

cleared to disable other maskable interrupts.

Timer/Event Counter 1 is operated in the same manner

but its related interrupt request flag is T1F (bit 4 of

INTC1) and its subroutine call location is 10H.

The time base interrupt is initialized by setting the time

base interrupt request flag (TBF; bit 5 of INTC1), that is

caused by a regular time base signal. After the interrupt

is enabled, and the stack is not full, and the TBF bit is

set, a subroutine call to location 14H occurs. The related

interrupt request flag (TBF) is reset and the EMI bit is

cleared to disable further maskable interrupts.

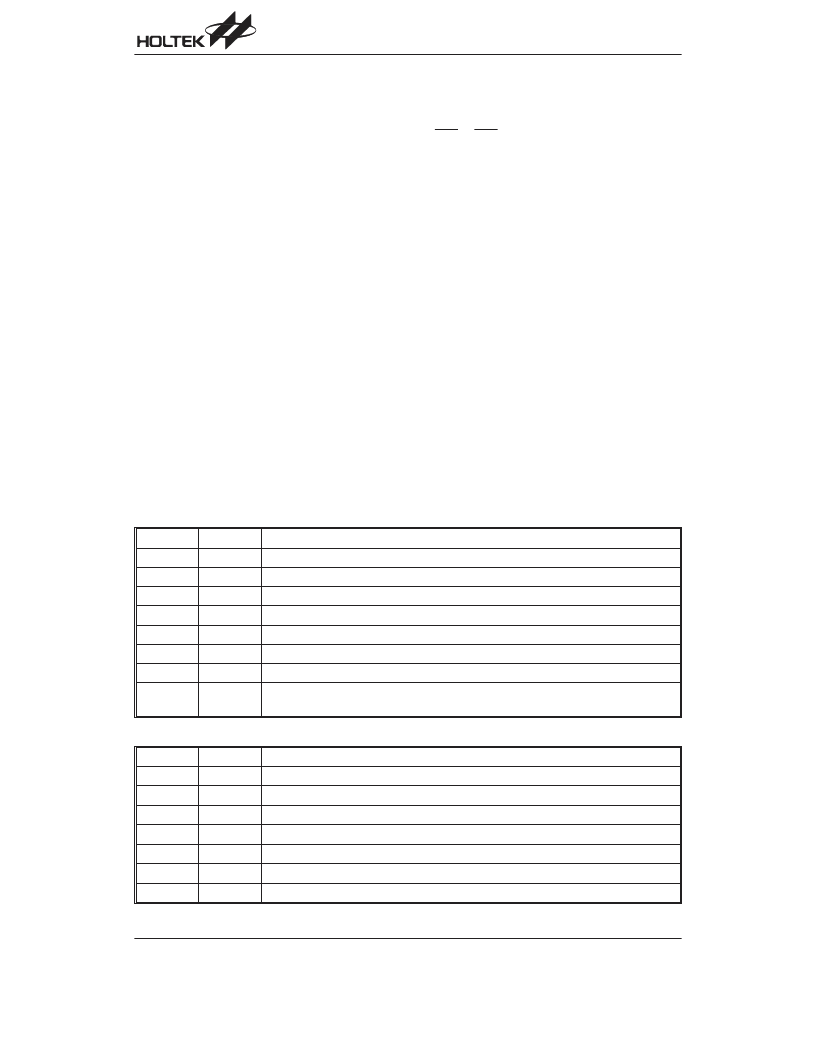

Bit No.

Label

Function

0

EMI

Control the master (global) interrupt (1=enabled; 0=disabled)

1

EEI0

Control the external interrupt 0 (1=enabled; 0=disabled)

2

EEI1

Control the external interrupt 1 (1=enabled; 0=disabled)

3

ET0I

Control the Timer/Event Counter 0 interrupt (1=enabled; 0=disabled)

4

EIF0

External interrupt 0 request flag (1=active; 0=inactive)

5

EIF1

External interrupt 1 request flag (1=active; 0=inactive)

6

T0F

Internal Timer/Event Counter 0 request flag (1=active; 0=inactive)

7

For test mode used only.

Must be written as 0 ; otherwise may result in unpredictable operation.

INTC0 (0BH) Register

Bit No.

Label

Function

0

ET1I

Control the Timer/Event Counter 1 interrupt (1=enabled; 0=disabled)

1

ETBI

Control the time base interrupt (1=enabled; 0:disabled)

2

ERTI

Control the real time clock interrupt (1=enabled; 0:disabled)

3, 7

Unused bit, read as 0

4

T1F

Internal Timer/Event Counter 1 request flag (1=active; 0=inactive)

5

TBF

Time base request flag (1=active; 0=inactive)

6

RTF

Real time clock request flag (1=active; 0=inactive)

INTC1 (1EH) Register

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT46R65 | A/D with LCD Type 8-Bit MCU |

| HT46R65-52 | A/D with LCD Type 8-Bit MCU |

| HT46R65-56 | A/D with LCD Type 8-Bit MCU |

| HT47C20L | 8-BIT MICROCONTROLLER |

| HT47C20 | 8-BIT MICROCONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT46CU25 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D Type 8-Bit MCU |

| HT46CU26 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D Type 8-Bit MCU with UART |

| HT46CU66 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D Type 8-Bit MCU with LCD |

| HT46CU66_11 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D Type 8-Bit MCU with LCD |

| HT46CU67 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D Type 8-Bit MCU with LCD |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。