- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385398 > HT24LC16 (Holtek Semiconductor Inc.) The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each PDF資料下載

參數(shù)資料

| 型號: | HT24LC16 |

| 廠商: | Holtek Semiconductor Inc. |

| 元件分類: | DRAM |

| 英文描述: | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| 中文描述: | 該CAT24FC02是一個2 KB的EEPROM的國內(nèi)256個8位每字舉辦的串行CMOS |

| 文件頁數(shù): | 5/11頁 |

| 文件大?。?/td> | 171K |

| 代理商: | HT24LC16 |

HT24LC16

Rev. 1.30

5

November 25, 2003

Current address read

The internal data word address counter maintains the

last address accessed during the last read or write op-

eration, incremented by one. This address stays valid

betweenoperationsaslongasthechippowerismain-

tained. The address roll over during read from the last

byteofthelastmemorypagetothefirstbyteofthefirst

page. The address roll over during write from the last

byte of the current page to the first byte of the same

page. Once the device address with the read/write se-

lect bit set to one is clocked in and acknowledged by

the EEPROM, the current address data word is seri-

ally clocked out. The microcontroller should respond

with a no ACK signal (high) followed by a stop condi-

tion (refer to Current read timing).

Random read

Arandom read requires a dummy byte write sequence

to load in the data word address which is then clocked

in and acknowledged by the EEPROM. The

microcontroller must then generate another start con-

dition. The microcontroller now initiates a current ad-

dress read by sending a device address with the

read/write select bit high. The EEPROM acknowl-

edges the device address and serially clocks out the

data word. The microcontroller should respond with a

no ACK signal (high) followed by a stop condition

(refer to Random read timing).

Sequential read

Sequential reads are initiated by either a current ad-

dress read or a random address read. After the

microcontroller receives a data word, it responds with

an acknowledgment. As long as the EEPROM re-

ceives an acknowledgment, it will continue to incre-

ment the data word address and serially clock out

sequential data words. When the memory address

limit is reached, the data word address will roll over

and the sequential read continues. The sequential

read operation is terminated when the microcontroller

responds with a no ACK signal (high) followed by a

stop condition.

2

) ( ! !

" "

! ) ( ! !

" "

4

.

(

4

3

)

4

4

5

2

) ( ! !

" "

(

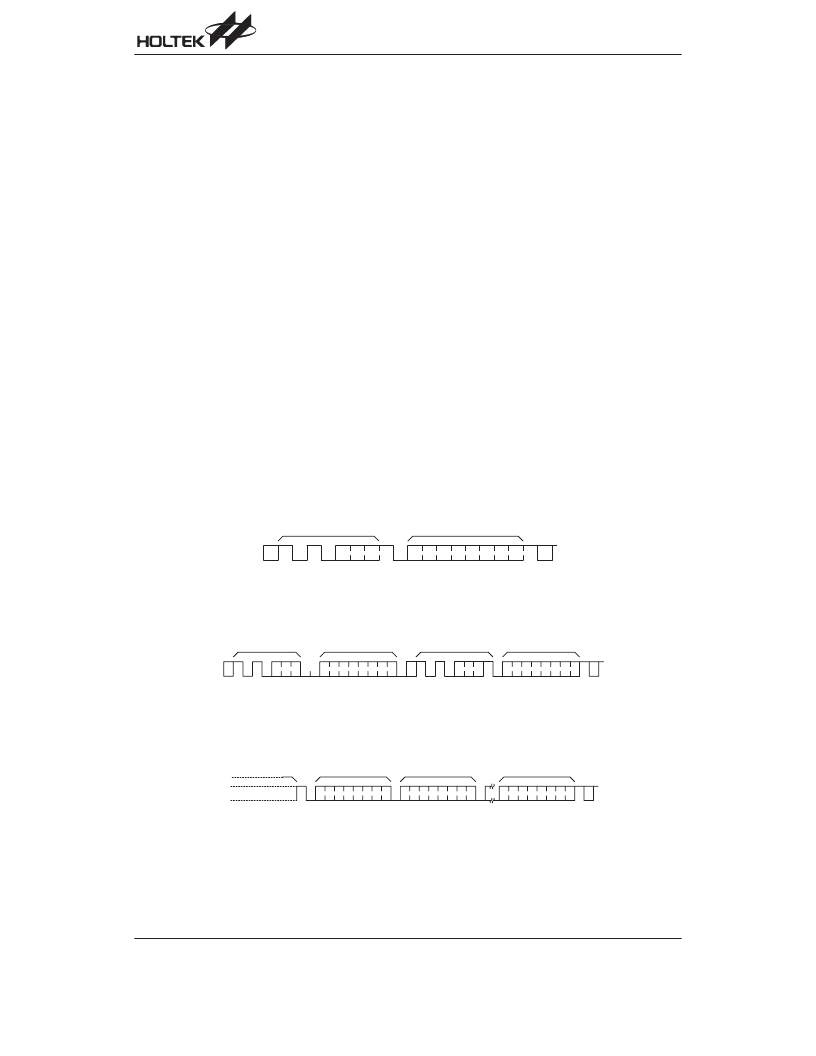

Random Read Timing

2

) ( ! !

" "

5

4

.

(

3

)

4

Current Read Timing

2

) ( ! !

" "

5

)

.

(

4

4

5

) 6

5

) 6 7

3

)

4

Sequential Read Timing

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT25LC512 | CMOS 64Kx8-Bit SPI Serial OTP EPROM |

| HT27C010 | 128K x 8-Bit CMOS OTP EPROM(128K x 8位 CMOS一次可編程EPROM) |

| HT27C020 | OTP CMOS 256Kx 8-Bit EPROM |

| HT27C040 | 512K x 8-Bit CMOS OTP EPROM(512K x 8位 CMOS一次可編程EPROM) |

| HT27C512 | OTP CMOS 64Kx 8-Bit EPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT24LC16(8DIP) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:I2C Serial EEPROM |

| HT24LC16(8SOIC) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:I2C Serial EEPROM |

| HT24LC16(8SOP) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

| HT24LC16-8DIP-A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

| HT24LC16-8SOP-A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

發(fā)布緊急采購,3分鐘左右您將得到回復。