- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371898 > HSP50016JC-52 (INTERSIL CORP) Digital Down Converter PDF資料下載

參數(shù)資料

| 型號(hào): | HSP50016JC-52 |

| 廠商: | INTERSIL CORP |

| 元件分類: | 數(shù)字信號(hào)處理外設(shè) |

| 英文描述: | Digital Down Converter |

| 中文描述: | 16-BIT, DSP-MIXER, PQCC44 |

| 封裝: | PLASTIC, LCC-44 |

| 文件頁數(shù): | 29/31頁 |

| 文件大小: | 209K |

| 代理商: | HSP50016JC-52 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁

3-226

RESET, IQSTRT Setup Time from CLK

t

RS

t

RH

t

DO

t

CCP

t

CCH

t

CCL

t

CDS

t

CDH

t

CLS

t

CHH

t

TCP

t

TH

t

TL

t

TRL

t

TDO

t

ATS

t

ATH

t

TCS

t

TCH

t

OE

t

OD

t

TOE

t

TOD

t

RF

Note 6

10

-

7

-

ns

RESET, IQSTRT Hold Time to CLK

Note 6

1

-

1

-

ns

CLK to I, Q, IQSTB, IQCLK Delay

-

15

-

12

ns

CCLK Period

100

-

100

-

ns

CCLK High

40

-

40

-

ns

CCLK Low

40

-

40

-

ns

CDATA, CSTB, CS Setup to CCLK

30

-

30

-

ns

CDATA, CSTB, CS Hold from CCLK

30

-

30

-

ns

CCLK Low Setup to CLK

Notes 6, 7

30

-

30

-

ns

CCLK High Hold from CLK

Notes 6, 7, 10

30

-

30

-

ns

TCK Period

Note 8

100

-

100

-

ns

TCK High

40

-

40

-

ns

TCK Low

40

-

40

-

ns

TRST Pulse Width

100

-

100

-

ns

TCK to TDO, Data Delay

-

30

-

30

ns

Setup Time On All Inputs to TCK

Note 9

30

-

30

-

ns

Hold Time On All Inputs from TCK

Note 9

30

-

30

-

ns

TCK Setup Time to CLK

Note 8

30

-

30

-

ns

TCK Hold Time from CLK

Note 8

30

-

30

-

ns

Output Enable Time from CLK

Note 10

-

18

-

12

ns

Output Disable Time from CLK

Note 10

-

18

-

12

ns

Output Enable Time from TCK

Note 10

-

32

-

32

ns

Output Disable Time from TCK

Note 10

-

32

-

32

ns

Output Rise, Fall Time

Note 10

-

5

-

5

ns

NOTES:

5. AC tests performed with C

L

= 40pF, I

OL

= 5mA, and I

OH

= -5mA. Input reference level for CLK, TRST is 2.0V, all other inputs 1.5V. Test V

IH

=

3.0V, V

IHC

= 4.0V, V

IL

= 0V; V

OH

= V

OL

= 2.5V.

6. These are asynchronous inputs; setup and hold times must only be maintained in order to predict which clock cycle they take effect internally.

7. Timing must only be maintained when Update bit is active in control word data being loaded.

8. Special Timing relationship between TCK and CLK is required for Test Instructions RUNBIST, EXTEST and INTEST.

9. All inputs except TRST, and only when TCK is driving internal clock.

10. Controlled via design or process parameters and not directly tested. Characterized upon initial design and after major process and/or design

changes.

AC Electrical Specifications

V

CC

= 5.0V

±

5%, T

A

= 0

o

to 70

o

C, (Note 5)

(Continued)

PARAMETER

SYMBOL

NOTES

-52(52.6)MHz

-75(76.9)MHz

UNITS

MIN

MAX

MIN

MAX

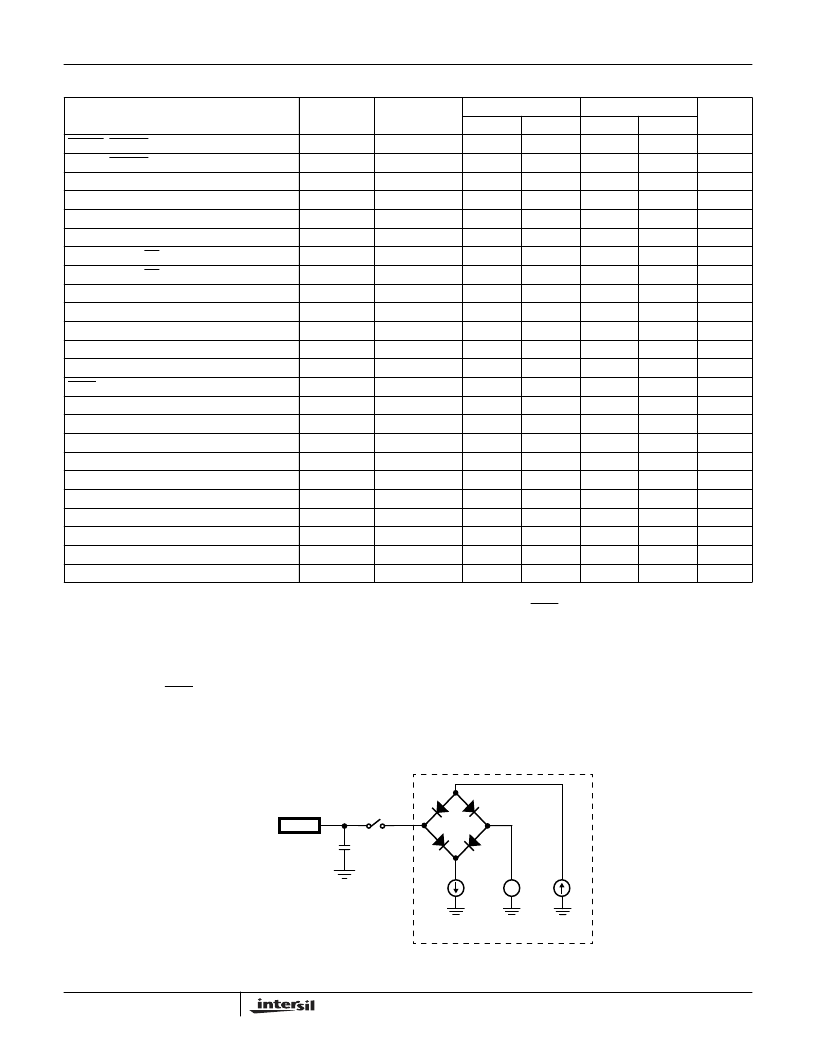

AC Test Load Circuit

NOTE:

Test head capacitance.

EQUIVALENT CIRCUIT

C

L

(NOTE)

I

OH

2.5V

I

OL

DUT

SWITCH S1 OPEN FOR I

CCSB

AND I

CCOP

S

1

±

HSP50016

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HSP50016JC-75 | Digital Down Converter |

| HSP50110JC-60 | Communications Tuner Circuit |

| HSP50306SC-25 | Digital QPSK Demodulator |

| HSP50306SC-2596 | Digital QPSK Demodulator |

| HSP50306SC-27 | Digital QPSK Demodulator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HSP50016JC-5296 | 制造商:Rochester Electronics LLC 功能描述:TAPE AND REEL OF HSP50016JC-52 - Bulk |

| HSP50016JC-75 | 制造商:Rochester Electronics LLC 功能描述:DIGITAL DOWN CONVERTER 44 PLCC 75MHZ COMM - Bulk |

| HSP50016JI-52 | 制造商:Rochester Electronics LLC 功能描述:DIGITAL DOWN CONVERTER 44 PLCC, 52MHZ, COMM,INDS - Bulk |

| HSP50016JM-5296R3571 | 制造商:Intersil Corporation 功能描述:ROCKWELL HSP50016JC-5296 W/BRAND,-55/+125C OP TEMP,ELECTR - Tape and Reel |

| HSP50016JM-52R3571 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。