- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385388 > HMS81032TL (Hynix Semiconductor Inc.) HYNIX SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS PDF資料下載

參數(shù)資料

| 型號(hào): | HMS81032TL |

| 廠商: | Hynix Semiconductor Inc. |

| 元件分類: | 8位微控制器 |

| 英文描述: | HYNIX SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| 中文描述: | Hynix半導(dǎo)體公司的8位單芯片微控制器 |

| 文件頁數(shù): | 55/77頁 |

| 文件大?。?/td> | 1112K |

| 代理商: | HMS81032TL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁當(dāng)前第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁

HMS81004E/08E/16E/24E/32E

52

JUNE 2001 Ver 1.00

14.5 BRK Interrupt

Software interrupt can be invoked by BRK instruction, which has

the lowest priority order.

Interrupt vector address of BRK is shared with the vector of

TCALL 0 (Refer to Program Memory Section). When BRK inter-

rupt is generated, B-flag of PSW is set to distinguish BRK from

TCALL 0.

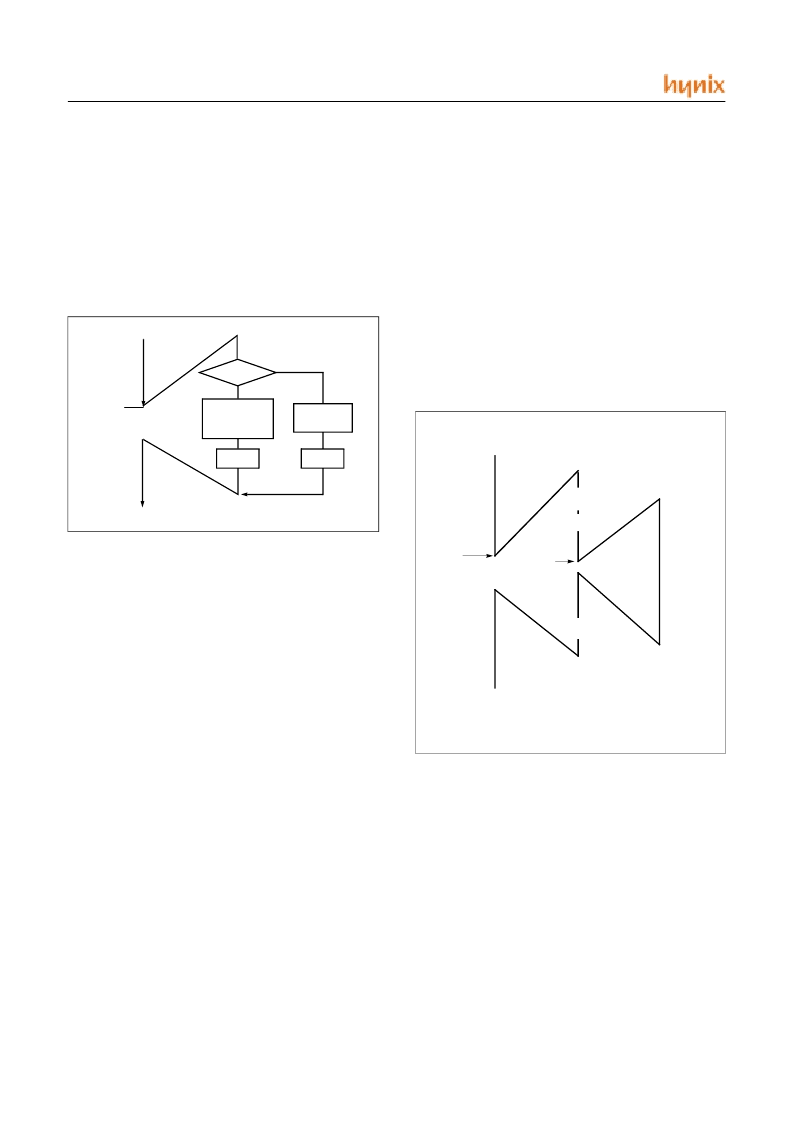

Each processing step is determined by B-flag as shown in Figure

14-5

Figure 14-5 Execution of BRK/TCALL0

14.6 Multi Interrupt

If two requests of different priority levels are received simulta-

neously, the request of higher priority level is serviced. If re-

quests of the interrupt are received at the same time

simultaneously, an internal polling sequence determines by hard-

ware which request is serviced.

However, multiple processing through software for special fea-

tures is possible. Generally when an interrupt is accepted, the I-

flag is cleared to disable any further interrupt. But as user sets I-

flag in interrupt routine, some further interrupt can be serviced

even if certain interrupt is in progress.

Example:

During Timer1 interrupt is in progress, INT1 interrupt

serviced without any suspend.

TIMER1: PUSH

A

X

Y

IENH,#40H

IENL,#00H

PUSH

PUSH

LDM

LDM

EI

:

:

;

Enable INT1 only

;

Disable other

;

Enable Interrupt

:

:

LDM

LDM

POP

POP

POP

RETI

IENH,#0FFH

IENL,#0FFH

Y

X

A

;

Enable all interrupts

Figure 14-6 Execution of Multi Interrupt

14.7 External Interrupt

The external interrupt on INT1 and INT2 pins are edge triggered

depending on the edge selection register IEDS (address 0D8

H

) as

shown in Figure14-7.

B-FLAG

BRK

INTERRUPT

ROUTINE

RETI

TCALL0

ROUTINE

RET

BRK or

TCALL0

=0

=1

enable INT1

disable other

TIMER 1

service

INT1

service

Main Program

service

Occur

TIMER1 interrupt

Occur

INT1

EI

enable INT1

enable other

In this example, the INT1 interrupt can be serviced without any

pending, even TIMER1 is in progress.

Because of re-setting the interrupt enable registers IENH,IENL

and master enable “EI” in the TIMER1 routine.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HMS81004E | HYNIX SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| HMS81008E | HYNIX SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| HMS81016E | HYNIX SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| HMS81024E | HYNIX SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| HMS81032E | HYNIX SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HMS81C2012A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CMOS Single-Chip 8-Bit Microcontroller with A/D Converter & VFD Driver |

| HMS81C2012AK | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CMOS Single-Chip 8-Bit Microcontroller with A/D Converter & VFD Driver |

| HMS81C2012ALQ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CMOS Single-Chip 8-Bit Microcontroller with A/D Converter & VFD Driver |

| HMS81C2012AQ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CMOS Single-Chip 8-Bit Microcontroller with A/D Converter & VFD Driver |

| HMS81C2020A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CMOS Single-Chip 8-Bit Microcontroller with A/D Converter & VFD Driver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。