- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370643 > HMP8156EVAL1 (Intersil Corporation) NTSC/PAL Encoders PDF資料下載

參數(shù)資料

| 型號(hào): | HMP8156EVAL1 |

| 廠商: | Intersil Corporation |

| 英文描述: | NTSC/PAL Encoders |

| 中文描述: | 的NTSC / PAL編碼器 |

| 文件頁數(shù): | 19/40頁 |

| 文件大?。?/td> | 563K |

| 代理商: | HMP8156EVAL1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

19

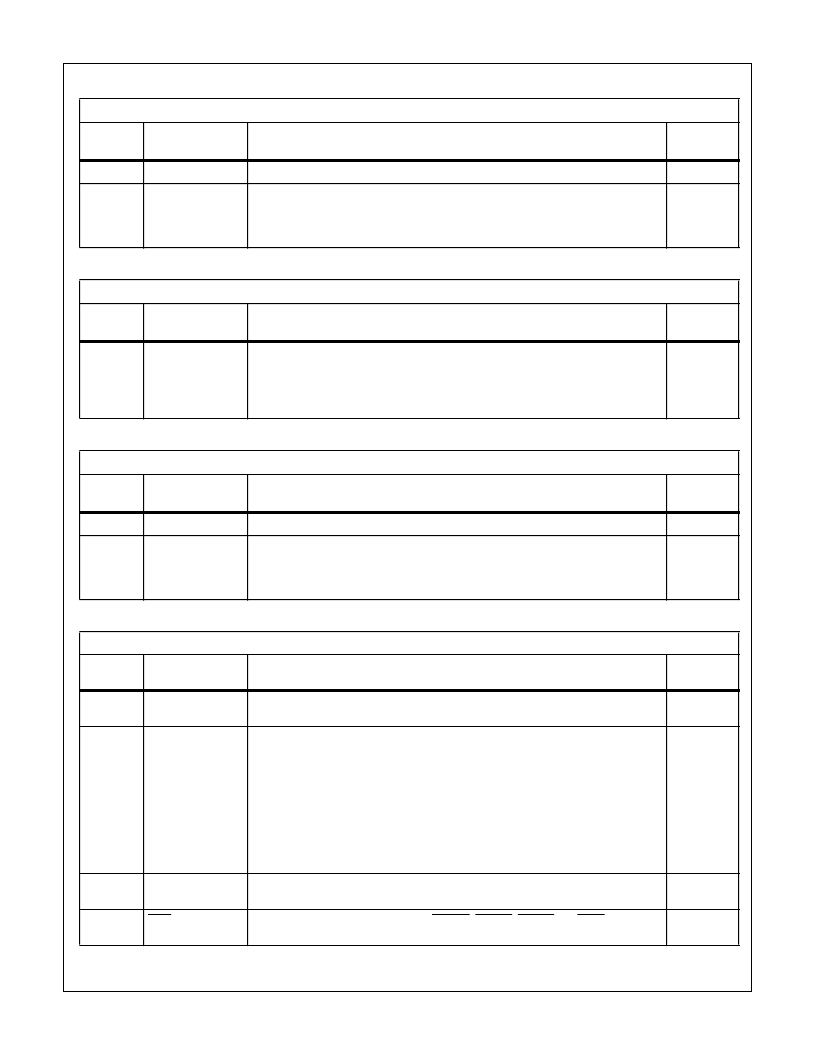

TABLE 25. DC RESTORE START TIME REGISTER

DESTINATION ADDRESS = 13

H

BIT

NUMBER

FUNCTION

DESCRIPTION

RESET

STATE

15 - 10

Not Used

XXXX XX

9 - 8

DC Restore

Programmable Start

Time

This register provides a programmable delay for the internal DC RES signal. The start

time of the DC RES pulse is set from the detection of horizontal sync in the video data.

DC RES is programmable in CLK increments and has a fixed 1 clock delay following the

falling edge of horizontal sync. This is the upper byte of the 10-bit word.

00

B

TABLE 26. DC RESTORE END TIME REGISTER

DESTINATION ADDRESS = 14

H

BIT

NUMBER

FUNCTION

DESCRIPTION

RESET

STATE

7 - 0

DC Restore

Programmable End

Time

This register provides a programmable delay for the internal DC RES signal. The end

time of the DC RES pulse is set from the detection of horizontal sync in the video data.

DC RES is programmable in CLK increments and has a fixed 1 clock delay following the

falling edge of horizontal sync. This signal is used to run the GATE B pin of the A/D con-

verter. This is the lower byte of the 10-bit word.

0101 0010

B

TABLE 27. DC RESTORE END TIME REGISTER

DESTINATION ADDRESS = 15

H

BIT

NUMBER

FUNCTION

DESCRIPTION

RESET

STATE

15 - 10

Not Used

XXXX XX

9 - 8

DC Restore

Programmable End

Time

This register provides a programmable delay for the external DC RES signal. The end

time of the DC RES pulse is set from the detection of horizontal sync in the video data.

DC RES is programmable in CLK increments and has a fixed 1 clock delay following the

falling edge of horizontal sync. This is the upper byte of the 10-bit word.

00

B

TABLE 28. OUTPUT FORMAT CONTROL REGISTER

DESTINATION ADDRESS = 16

H

BIT

NUMBER

FUNCTION

DESCRIPTION

RESET

STATE

7

Square Pixel/ITU-R

BT601 Select

When “1”, Square pixel output is selected, when “0” ITU-R BT601 output rate is selected.

0

B

6, 5, 4

Output Field Control

“FLD_CONT(2-0)”

These bits control the field capture rate of the HMP8112. The user can select every 4th

field, every other field or every field of video to be output to the data port.

000 = No Capture Enabled

001 = Capture every 4th field

010 = Capture every 2nd field

011 = Capture every 2nd odd field

100 = Capture every 2nd even field

101 = Capture every odd field

110 = Capture every even field

111 = Capture all fields

000

B

3

8/16 output Select

When “1”, the 8-bit Burst Transfer output mode is selected. When “0”, the 16-bit Synchro-

nous Pixel Transfer output mode is selected.

0

B

2

OEN

This bit enables the Y(7-0), CbCr(7-0), ACTIVE, HSYNC, VSYNC and DVLD outputs.

1 = Outputs enabled; 0 = three-stated.

0

B

HMP8112

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HMP8156EVAL2 | NTSC/PAL Encoders |

| HMP8156 | NTSC/PAL Encoder |

| HMP8156ACN | NTSC/PAL Encoders |

| HMP8156CN | NTSC/PAL Encoder |

| HMS30C7110 | Multipurpose Network Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HMP8156EVAL2 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HMP8170 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:NTSC/PAL Video Encoder |

| HMP8170_03 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:NTSC/PAL Video Encoder |

| HMP8170CN | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:NTSC/PAL Video Encoder |

| HMP8170EVAL1 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:NTSC/PAL Video Encoder |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。