- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384418 > HI-8685PJT-10 (HOLT INTEGRATED CIRCUITS INC) ARINC INTERFACE DEVICE ARINC 429& 561 SERIAL DATA TO 16-BIT PARALLEL DATA PDF資料下載

參數(shù)資料

| 型號(hào): | HI-8685PJT-10 |

| 廠商: | HOLT INTEGRATED CIRCUITS INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | ARINC INTERFACE DEVICE ARINC 429& 561 SERIAL DATA TO 16-BIT PARALLEL DATA |

| 中文描述: | 1 CHANNEL(S), SERIAL COMM CONTROLLER, PQCC28 |

| 封裝: | PLASTIC, LCC-28 |

| 文件頁(yè)數(shù): | 3/10頁(yè) |

| 文件大小: | 239K |

| 代理商: | HI-8685PJT-10 |

HI-8685, HI-8686

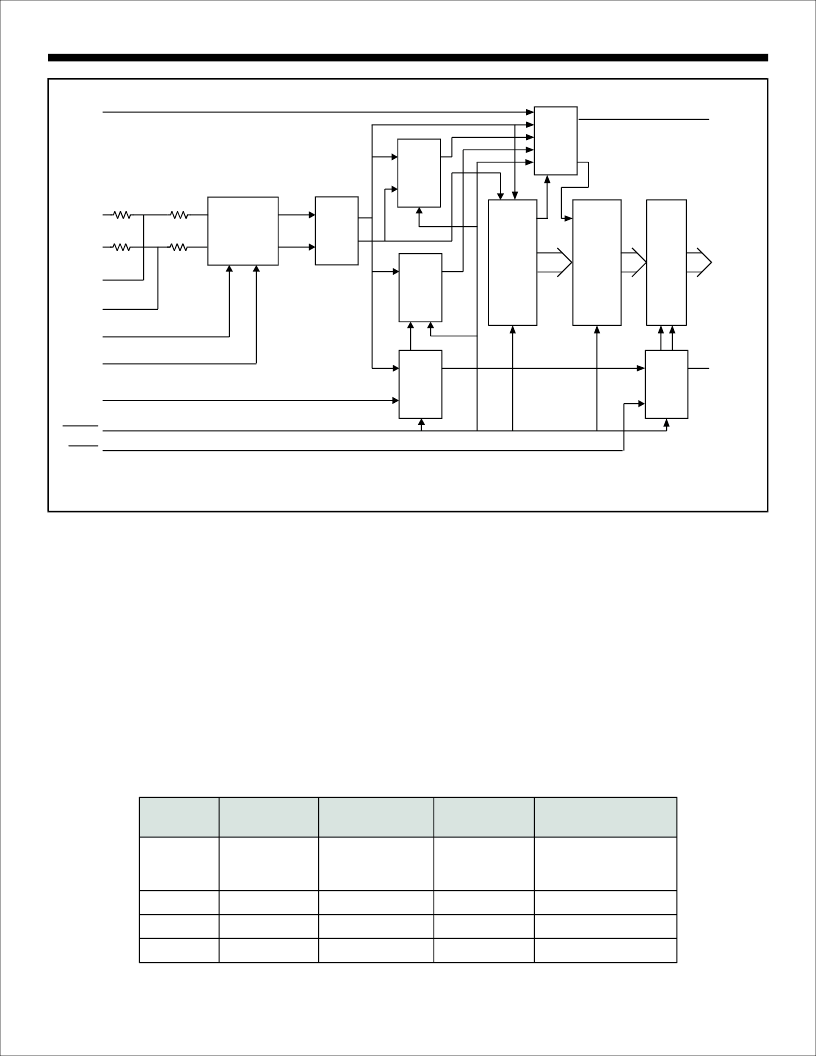

PROTOCOLDETECTION

The ARINC clock and One/Zero data that are derived from

the

outputsof the built-in line receiver isillustrated in

Figure 3. The resulting steam of digitaldata is shifted into a

32-bitinputregister.

The ARINC clock and One/Zero data can also be created

from the TESTA and TESTB inputs as shown in Figure 4.

When either test input is high, the built-in analog line driver

isdisabled.

digital

For ARINC 561 operation, the TESTA and TESTB digitalin-

putdatastreamsmustbederivedfromtheARINC561data,

clockandsyncwithexternallogic.

GAPDETECTION

The end of a data word is detected by an internal counter

that times out when a data One or Zero is not received for a

period equal to 16 cycles of the GAPCLK signal. The gap

detection time may vary between 16 and 17 cycles of the

GAPCLK signal since the incoming data and GAPCLK are

not usually synchronous inputs. The required frequency of

GAPCLK is a function of the mininum gap time specified for

the type of ARINC data being received. Table 1 indicates

typical frequencies that may be used for the various data

ratesnormallyencountered.

BIT

COUNT

PARITY

DETECT

GAP

DETECT

32-BIT

SHIFT

REG.

32-BIT

RECEIVE

BUFFER

32-BIT

TO

16-BIT

MUX

ERROR

DETECT

CLOCK

&

DATA

DETECT

PARITY

ENB

RINB

TESTA

TESTB

GAPCLK

RESET

BYTE

COUNT

READ

DATA RDY

ERROR

32

16

32

Figure 1. Block Diagram

ESD

PROTECTION

&

LINE

RECEIVER

DATABUS

TYPE

BIT PERIOD

( s)

MINIMUM GAP

( s)

GAP CLOCK

MHz

GAP DETECTION

TIME ( s)

429

10

45

0.75

1.0

1.5

21.3 - 22.7

16 - 17

10.7 - 11.3

429

69 - 133

310 - 599

0.1

160 - 170

575

69 - 133

310 - 599

0.1

160 - 170

561

69 - 133

103 - 200

0.2

80 - 85

Table 1 - Typical Gap Detection Times

FUNCTIONAL DESCRIPTION (cont.)

RXA

RXB

10K

BIT 32

BIT 32

RINA

10K

D0 - D15

25K

25K

RINB-10

RINA-10

DATA

CLK

HOLT INTEGRATED CIRCUITS

3

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HI-8685 | 384 MCELL 3 VOLT ZERO POWER ISP CPLD - NOT RECOMMENDED for NEW DESIGN |

| HI-8685PJT | ARINC INTERFACE DEVICE ARINC 429& 561 SERIAL DATA TO 16-BIT PARALLEL DATA |

| HI-8685PSI | ARINC INTERFACE DEVICE ARINC 429& 561 SERIAL DATA TO 16-BIT PARALLEL DATA |

| HI-8685PSI-10 | 384 MCELL 3 VOLT ZERO POWER ISP CPLD - NOT RECOMMENDED for NEW DESIGN |

| HI-8685PST | ARINC INTERFACE DEVICE ARINC 429& 561 SERIAL DATA TO 16-BIT PARALLEL DATA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HI-8733 | 制造商:HANNA INSTRUMENTS 功能描述:CONDUCTIVITY METER |

| HI-8733N | 制造商:HANNA INSTRUMENTS 功能描述:CONDUCTIVITY METER 制造商:HANNA INSTRUMENTS 功能描述:CONDUCTIVITY METER; Conductivity Range:0S/cm to 1999S/cm; Accuracy %:1%; Calibration Type:Temperature; External Height:185mm; External Width:82mm; External Depth:45mm; Weight:355g; Accuracy: 1% full scale; Battery Lifetime:100h; |

| HI8783PSI | 制造商:Holt Integrated Circuits 功能描述:ARINC Interface Device 20-Pin SOIC W |

| HI-8783PSIF | 制造商:Holt Integrated Circuits 功能描述: |

| HI882 | 制造商:HSMC 制造商全稱:HSMC 功能描述:NPN EPITAXIAL PLANAR TRANSISTOR |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。