- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384403 > HFA3860IV (HARRIS SEMICONDUCTOR) 11 Mbps Direct Sequence Spread Spectrum Baseband Processor PDF資料下載

參數(shù)資料

| 型號: | HFA3860IV |

| 廠商: | HARRIS SEMICONDUCTOR |

| 元件分類: | 無繩電話/電話 |

| 英文描述: | 11 Mbps Direct Sequence Spread Spectrum Baseband Processor |

| 中文描述: | TELECOM, CELLULAR, BASEBAND CIRCUIT, PQFP48 |

| 文件頁數(shù): | 13/40頁 |

| 文件大小: | 250K |

| 代理商: | HFA3860IV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

4-13

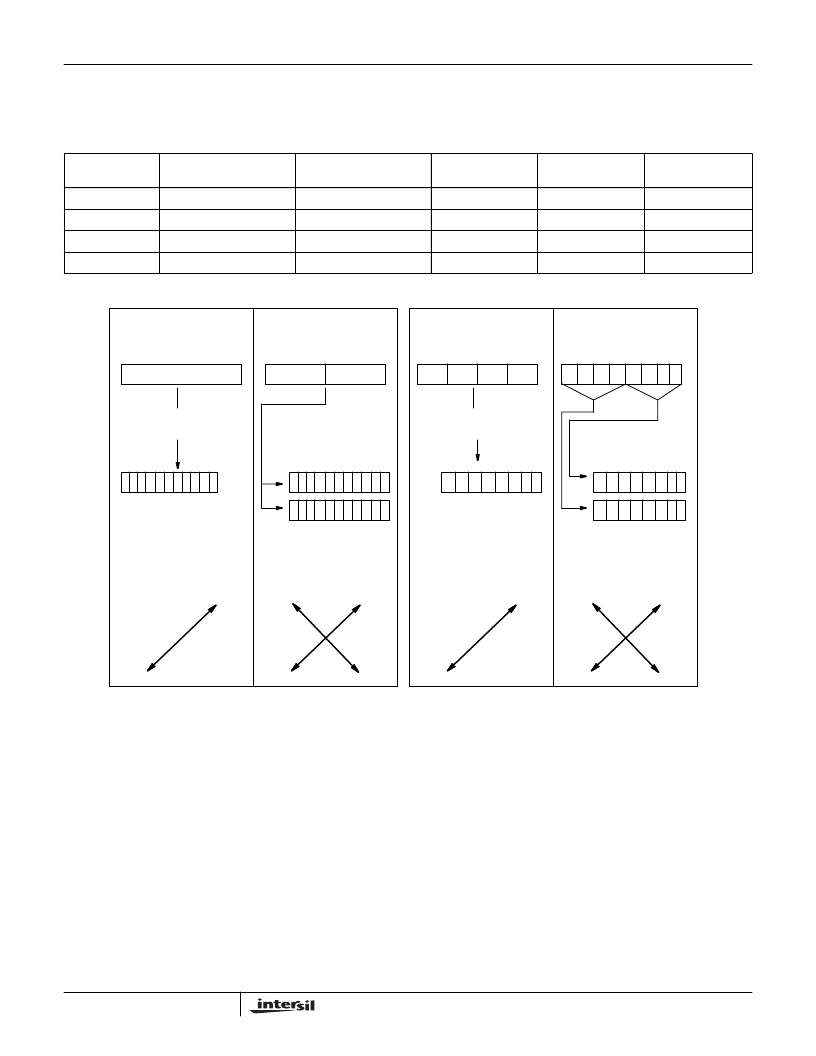

Table 7 shows examples of the bit rates and the symbol

rates and Figure 8 shows the modulation schemes.

The modulator is completely independent from the

demodulator, allowing the PRISM baseband processor to be

used in full duplex operation.

Header/Packet Description

The HFA3860 is designed to handle continuous or

packetized Direct Sequence Spread Spectrum (DSSS) data

transmissions. The HFA3860 generates its own preamble

and header information.

The device uses a synchronization preamble of up to 256

symbols, and a header that includes five fields. The

preamble is all 1's (before entering the scrambler). The

actual transmitted pattern of the preamble will be

randomized by the scrambler. The preamble is always

transmitted as a DBPSK waveform.

The five fields for the header shown in Figure 9 are:

Start Frame Delimiter (SFD) Field (16 Bits) -

This

carries the synchronization to establish the link frame timing.

The HFA3860 will not declare a valid data packet, even if it

PN acquires, unless it detects the SFD. The HFA3860

receiver is programmed to time out searching for the SFD via

CR15. The timer starts counting the moment that initial PN

synchronization has been established from the preamble.

field

Signal Field (8 Bits) -

This field indicates what data rate the

data packet that follows the header will be. The HFA3860

receiver looks at the signal field to determine whether it

needs to switch from DBPSK demodulation into DQPSK or

B/QMBOK demodulation at the end of the always DBPSK

preamble and header fields.

Service Field (8 Bits) -

This field is currently unassigned

and can be utilized as required by the user. Set to 00h for

TABLE 7. BIT RATE TABLE EXAMPLES FOR MCLK = 44MHz

DATA

MODULATION

A/D SAMPLE CLOCK

(MHZ)

TX SETUP CR 20

BITS 1, 0

RX STATUS CR 24

BITS 7, 6

DATA RATE (Mbps)

SYMBOL RATE

(MSPS)

DBPSK

44

00

00

1

1

DQPSK

44

01

01

2

1

BMBOK

44

10

10

5.5

1.375

QMBOK

44

11

11

11

1.375

802.11 DSSS BPSK

1 MB/S

BARKER

802.11 DSSS QPSK

2 MB/S

BARKER

5.5 MB/S BMBOK

MODIFIED

WALSH FUNCTIONS

11 MB/S QMBOK

MODIFIED

WALSH FUNCTIONS

DATA

IOUT

QOUT

CHIP

RATE

1 BIT ENCODED TO ONE OF

2 CODE WORDS

(TRUE/INVERSE)

2 BITS ENCODED

TO ONE OF

4 CODE WORDS

4 BITS ENCODED TO ONE OF

16 MODIFIED WALSH

CODE WORDS

8 BITS ENCODED TO

ONE OF

256 MODIFIED WALSH

CODE WORDS

SYMBOL

RATE

I vs Q

11 MC/S

11 MC/S

11 MC/S

11 MC/S

1 MS/S

1 MS/S

1.375 MS/S

1.375 MS/S

11 CHIPS

11 CHIPS

8 CHIPS

8 CHIPS

FIGURE 8. MODULATION MODES

HFA3860

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HFA3860IV96 | 11 Mbps Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861A | Direct Sequence Spread Spectrum Baseband Processor(直接序列擴頻基帶處理器) |

| HFA3861B | Direct Sequence Spread Spectrum Baseband Processor(直接序列擴譜基帶處理器) |

| HFA3861 | Direct Sequence Spread Spectrum (DSSS) baseband processor(直接序列擴頻基帶處理器) |

| HFA3861IV | Direct Sequence Spread Spectrum Baseband Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HFA3860IV WAF | 制造商:Harris Corporation 功能描述: |

| HFA3860IV96 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:11 Mbps Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861A | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processo |

| HFA3861AIN | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processo |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。