- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370458 > HD404369 (Hitachi,Ltd.) 4-bit HMCS400-Series microcomputer PDF資料下載

參數(shù)資料

| 型號: | HD404369 |

| 廠商: | Hitachi,Ltd. |

| 英文描述: | 4-bit HMCS400-Series microcomputer |

| 中文描述: | 4位HMCS400系列微機(jī) |

| 文件頁數(shù): | 12/115頁 |

| 文件大小: | 452K |

| 代理商: | HD404369 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁

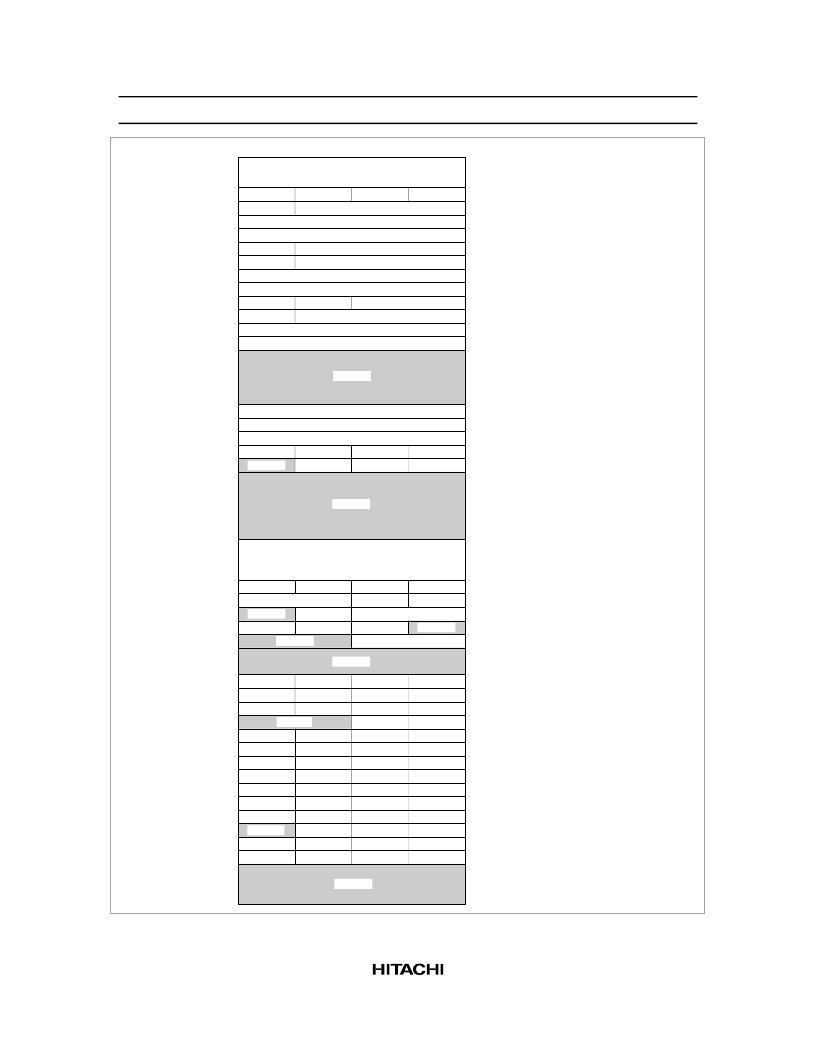

HD404369 Series

12

$000

$003

PMRA $004

SMR $005

SRL $006

SRU $007

TMA $008

TMB1 $009

TRBL/TWBL $00A

TRBU/TWBU $00B

MIS $00C

TMC $00D

TRCL/TWCL $00E

TRCU/TWCU $00F

ACR $016

ADRL $017

ADRU $018

AMR1$019

AMR2 $01A

$020

$023

PMRB $024

PMRC $025

TMB2 $026

SSR1 $027

SSR2 $028

DCD0 $02C

DCD1 $02D

DCD2 $02E

DCD3 $02F

DCR0 $030

DCR1 $031

DCR2 $032

DCR3 $033

DCR4 $034

DCR5 $035

DCR6 $036

DCR7 $037

DCR8 $038

DCR9 $039

$03F

Bit 3

Bit 2

Bit 1

Interrupt control bits area

D

3

/BUZZ

R0

0

/

SCK

R0

3

/TOC

Serial transmit clock speed selection

Serial data register (lower digit)

Serial data register (upper digit)

Clock source selection (timer A)

Clock source selection (timer B)

Timer B register (lower digit)

Timer B register (upper digit)

R0

2

/SO

SO PMOS control

Interrupt frame period selection

Clock source selection (timer C)

Timer C register (lower digit)

Timer C register (upper digit)

Analog channel selection

A/D data register (lower digit)

A/D data register (upper digit)

R3

2

/AN

2

R5/AN

8

–AN

11

R4/AN

4

–AN

7

Register flag area

Port D

3

DCD

Port D

7

DCD

Port D

11

DCD

Port D

2

DCD

Port D

6

DCD

Port D

10

DCD

Not used

Port D

1

DCD

Port D

5

DCD

Port D

9

DCD

Port D

13

DCD

Port D

0

DCD

Port D

4

DCD

8

DCD

Port D

12

DCD

Port R0

3

DCR

Port R1

3

DCR

Port R2

3

DCR

Port R3

3

DCR

Port R4

3

DCR

Port R5

3

DCR

Port R6

3

DCR

Not used

Port R0

2

DCR

Port R1

2

DCR

Port R2

2

DCR

Port R3

2

DCR Port R3

1

DCR Port R3

0

DCR

Port R4

2

DCR

Port R5

2

DCR

Port R6

2

DCR

Port R7

2

DCR

Port R8

2

DCR

Port R9

2

DCR

Port R0

1

DCR

Port R1

1

DCR

Port R2

1

DCR

Port R4

1

DCR

Port R5

1

DCR

Port R6

1

DCR

Port R7

1

DCR

Port R8

1

DCR

Port R9

1

DCR

Port R0

0

DCR

Port R1

0

DCR

Port R2

0

DCR

Port R4

0

DCR

Port R5

0

DCR

Port R6

0

DCR

Port R7

0

DCR

Port R8

0

DCR

Port R9

0

DCR

1.

2.

3.

4.

5.

6.

7.

8.

9.

Bit 0

1

2

*

*

3

2

*

*

Timer-A/time-base

Auto-reload on/off

Pull-up MOS control

A/D conversion time

SO output level control in idle states

Serial clock source selection

Input capture selection

32-kHz oscillation stop

32-kHz oscillation division ratio

Notes:

R0

1

/SI

Not used

R3

3

/AN

3

R3

1

/AN

1

R3

0

/AN

0

4

*

Port R8

3

DCR

Port R9

3

DCR

D

4

/

STOPC

Buzzer output

Not used

*

8

D

2

/EVNB

*

7

*

9

D

1

/

INT

1

*

5

EVNB detection edge selection

Clock select

Clock division ratio selection

D

0

/

INT

0

*

6

Not used

Not used

Not used

Not used

Not used

Not used

Figure 5 Special Function Register Area

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HD404369H | 4-bit HMCS400-Series microcomputer |

| HD404369S | 4-bit HMCS400-Series microcomputer |

| HD404369F | 4-bit HMCS400-Series microcomputer |

| HD404372 | Low-Voltage AS Microcomputers with On-Chip A/D Converter(帶片上A/D轉(zhuǎn)換器的低壓微計算機(jī)) |

| HD404082 | Low-Voltage AS Microcomputers with On-Chip A/D Converter(帶片上A/D轉(zhuǎn)換器的低壓微計算機(jī)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HD404369F | 制造商:HITACHI 制造商全稱:Hitachi Semiconductor 功能描述:4-bit HMCS400-Series microcomputer |

| HD404369H | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:microcomputer has an A/D converter |

| HD404369S | 制造商:HITACHI 制造商全稱:Hitachi Semiconductor 功能描述:4-bit HMCS400-Series microcomputer |

| HD404369SERIES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| HD404372 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:HMCS43XXFamily User's Manual/Device |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。