- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385356 > HCTS75K (Intersil Corporation) Quadruple Bus Buffer Gates With 3- State Outputs 14-CDIP -55 to 125 PDF資料下載

參數(shù)資料

| 型號(hào): | HCTS75K |

| 廠商: | Intersil Corporation |

| 英文描述: | Quadruple Bus Buffer Gates With 3- State Outputs 14-CDIP -55 to 125 |

| 中文描述: | 輻射加固雙2位雙穩(wěn)態(tài)透明鎖存器 |

| 文件頁數(shù): | 1/9頁 |

| 文件大?。?/td> | 136K |

| 代理商: | HCTS75K |

470

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

|

Copyright

Intersil Corporation 1999

HCTS75MS

Radiation Hardened

Dual 2-Bit Bistable Transparent Latch

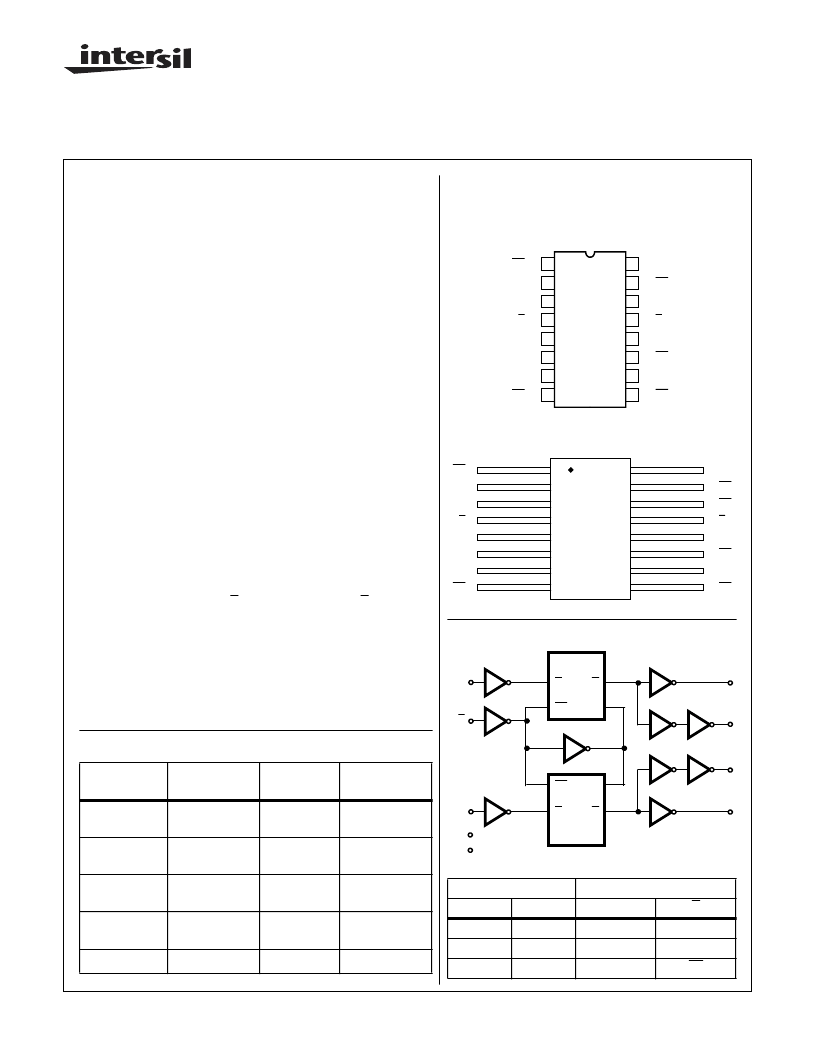

Pinouts

16 LEAD CERAMIC DUAL-IN-LINE

METAL SEAL PACKAGE (SBDIP)

MIL-STD-1835 CDIP2-T16, LEAD FINISH C

TOP VIEW

16 LEAD CERAMIC METAL SEAL FLATPACK PACKAGE

(FLATPACK) MIL-STD-1835 CDFP4-F16, LEAD FINISH C

TOP VIEW

Functional Diagram

TRUTH TABLE

INPUTS

OUTPUTS

D

E

Q

Q

L

H

L

H

H

H

H

L

X

L

Q0

Q0

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

Q0

D0

D1

E

VCC

D0

Q1

D1

Q0

Q1

E

GND

Q0

Q0

Q1

Q1

1

1

1

2

2

2

2

1

1

1

2

2

2

1

2

3

4

5

6

7

8

1

16

15

14

13

12

11

10

9

Q0

D0

D1

E

VCC

D0

Q1

D1

Q0

Q1

E

GND

Q0

Q0

Q1

Q1

1

1

1

2

2

2

2

1

1

1

2

2

2

1

LATCH 0

D

LE

LE

Q

LATCH 1

D

LE

LE

Q

16(10

1(11

14(8

15(9

D0

E

D1

VCC

GND

2(6)

13(4)

3(7)

5

12

Features

3 Micron Radiation Hardened SOS CMOS

Total Dose 200K RAD (Si)

SEP Effective LET No Upsets: >100 MEV-cm

2

/mg

Single Event Upset (SEU) Immunity < 2 x 10

-9

Errors/Bit-Day

(Typ)

Dose Rate Survivability: >1 x 10

12

RAD (Si)/s

Dose Rate Upset >10

10

RAD (Si)/s 20ns Pulse

Latch-Up Free Under Any Conditions

Military Temperature Range: -55

o

C to +125

o

C

Significant Power Reduction Compared to LSTTL ICs

DC Operating Voltage Range: 4.5V to 5.5V

LSTTL Input Compatibility

- VIL = 0.8V Max

- VIH = VCC/2 Min

Input Current Levels Ii

≤

5

μ

A at VOL, VOH

Description

The Intersil HCTS75MS is a Radiation Hardened dual 2-bit

bistable transparent latch. Each of the two latches are controlled

by a separate enable input (E) which are active low. E low latches

the output state.

The HCTS75MS utilizes advanced CMOS/SOS technology to

achieve high-speed operation. This device is a member of radia-

tion hardened, high-speed, CMOS/SOS Logic Family.

The HCTS75MS is supplied in a 16 lead Ceramic flatpack

(K suffix) or a SBDIP Package (D suffix).

Ordering Information

PART

NUMBER

TEMPERATURE

RANGE

SCREENING

LEVEL

PACKAGE

HCTS75DMSR

-55

o

C to +125

o

C

Intersil Class

S Equivalent

16 Lead SBDIP

HCTS75KMSR

-55

o

C to +125

o

C

Intersil Class

S Equivalent

16 Lead Ceramic

Flatpack

HCTS75D/

Sample

+25

o

C

Sample

16 Lead SBDIP

HCTS75K/

Sample

+25

o

C

Sample

16 Lead Ceramic

Flatpack

HCTS75HMSR

+25

o

C

Die

Die

September 1995

Spec Number

518625

File Number

3189.1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HCTS75KMSR | Quadruple Bus Buffer Gates With 3- State Outputs 14-CFP -55 to 125 |

| HCTS75MS | Quadruple Bus Buffer Gates With 3-State Outputs 20-LCCC -55 to 125 |

| HCTS75HMSR | Radiation Hardened Dual 2-Bit Bistable Transparent Latch |

| HD-6409883 | CMOS Manchester Encoder-Decoder |

| HD08 | Bridge Rectifier; Repetitive Reverse Voltage Max, Vrrm:200V; Package/Case:TO-126; Current Rating:4A; Mounting Type:Through Hole |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HCTS75KMSR | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened Dual 2-Bit Bistable Transparent Latch |

| HCTS75MS | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened Dual 2-Bit Bistable Transparent Latch |

| HCTS85D | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened 4-Bit Magnitude Comparator |

| HCTS85DMSR | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened 4-Bit Magnitude Comparator |

| HCTS85HMSR | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened 4-Bit Magnitude Comparator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。