- 您現在的位置:買賣IC網 > PDF目錄384348 > GS8170DW72C-300 (GSI TECHNOLOGY) 18Mb ヒ1x1Dp CMOS I/O Double Late Write SigmaRAM PDF資料下載

參數資料

| 型號: | GS8170DW72C-300 |

| 廠商: | GSI TECHNOLOGY |

| 元件分類: | DRAM |

| 英文描述: | 18Mb ヒ1x1Dp CMOS I/O Double Late Write SigmaRAM |

| 中文描述: | 256K X 72 STANDARD SRAM, 1.8 ns, PBGA209 |

| 封裝: | 14 X 22 MM, 1 MM PITCH, BGA-209 |

| 文件頁數: | 15/27頁 |

| 文件大小: | 827K |

| 代理商: | GS8170DW72C-300 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁

GS8170DW36/72C-333/300/250/200

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

Rev: 2.04 5/2005

15/27

2002, GSI Technology, Inc.

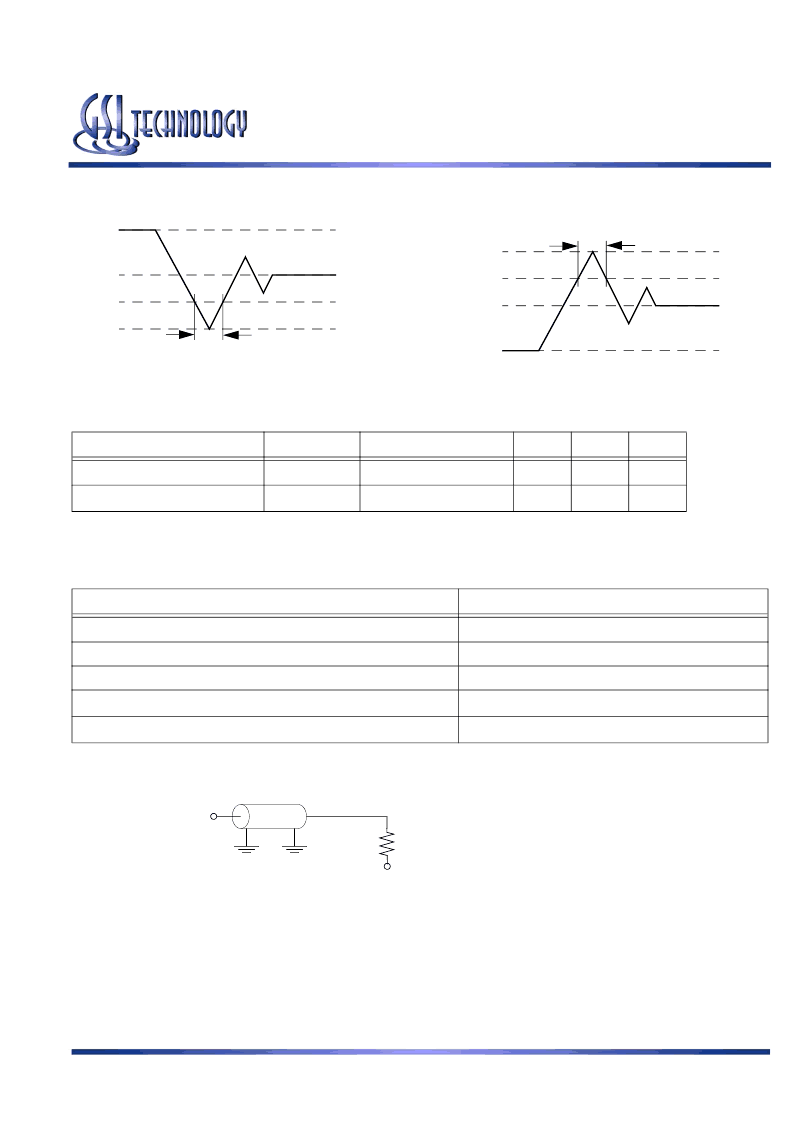

20% tKC

V

SS

– 1.0 V

50%

V

SS

V

IH

Undershoot Measurement and Timing

Overshoot Measurement and Timing

20% tKC

V

DD

+ 1.0 V

50%

V

DD

V

IL

Capacitance

(T

A

= 25

o

C, f = 1 MH

Z

, V

DD

Parameter

Symbol

Test conditions

Typ.

Max.

Unit

Input Capacitance

C

IN

V

IN

= 0 V

4

5

pF

Output Capacitance

C

OUT

V

OUT

= 0 V

6

7

pF

Note:

This parameter is sample tested.

AC Test Conditions

Parameter

Conditions

Input high level

V

DD

Input low level

0 V

Max. input slew rate

2 V/ns

Input reference level

V

DD

/2

Output reference level

V

DDQ

/2

DQ

VT = V

DDQ

/2

50

RQ = 250

(HSTL I/O)

AC Test Load Diagram

= 1.8 V)

相關PDF資料 |

PDF描述 |

|---|---|

| GS8170DW72C-300I | 18Mb ヒ1x1Dp CMOS I/O Double Late Write SigmaRAM |

| GS8170DW72C-333 | 18Mb ヒ1x1Dp CMOS I/O Double Late Write SigmaRAM |

| GS8170DW72C-333I | 18Mb ヒ1x1Dp CMOS I/O Double Late Write SigmaRAM |

| GS8170LW36AC | 18Mb ヒ1x1Lp CMOS I/O Late Write SigmaRAM |

| GS8321Z18E-133IV | 36Mb Pipelined and Flow Through Synchronous NBT SRAMs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| GS8170LW36AC-300I | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 1.8V 18MBIT 512KX36 1.8NS 209FBGA - Trays |

| GS8170LW36AGC-250 | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 1.8V 18MBIT 512KX36 2.1NS 209FBGA - Trays |

| GS8170LW36AGC-250I | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 1.8V 18MBIT 512KX36 2.1NS 209FBGA - Trays |

| GS8170LW36AGC-350 | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 1.8V 18MBIT 512KX36 1.7NS 209FBGA - Trays |

| GS8170LW36AGC-350I | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 1.8V 18MBIT 512KX36 1.7NS 209FBGA - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復。