- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄375849 > FM3164-S (Electronic Theatre Controls, Inc.) Integrated Processor Companion with Memory PDF資料下載

參數(shù)資料

| 型號(hào): | FM3164-S |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Integrated Processor Companion with Memory |

| 中文描述: | 綜合處理器與記憶體伴侶 |

| 文件頁(yè)數(shù): | 7/22頁(yè) |

| 文件大小: | 286K |

| 代理商: | FM3164-S |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)

However, an advantage of combining a clock

function with FRAM memory is that data is not lost

regardless of the backup power source.

When a battery is used as a backup source, V

DD

must

be applied prior to inserting the battery to prevent

battery drain. Once V

DD

is applied and a battery is

inserted, the current drain on the battery is

guaranteed to be less than I

BAK

(max).

FM3104/16/64/256

Rev 0.2

May 2003

Page 7 of 22

Trickle Charger

To facilitate capacitor backup the VBAK pin can

optionally provide a trickle charge current. When the

VBC bit, register 0Bh bit 2, is set to 1 the VBAK pin

will source approximately 4 μA until VBAK reaches

VDD or 3.75V whichever is less. In 3V systems, this

charges the capacitor to VDD without an external

diode and resistor charger. In 5V systems, it provides

the same convenience and also prevents the user from

exceeding

the

VBAK

specification.

!

Note: systems using lithium batteries should clear

the VBC bit to 0 to prevent battery charging. The

VBAK circuitry includes an internal 1 K

series

resistor as a safety element.

maximum

voltage

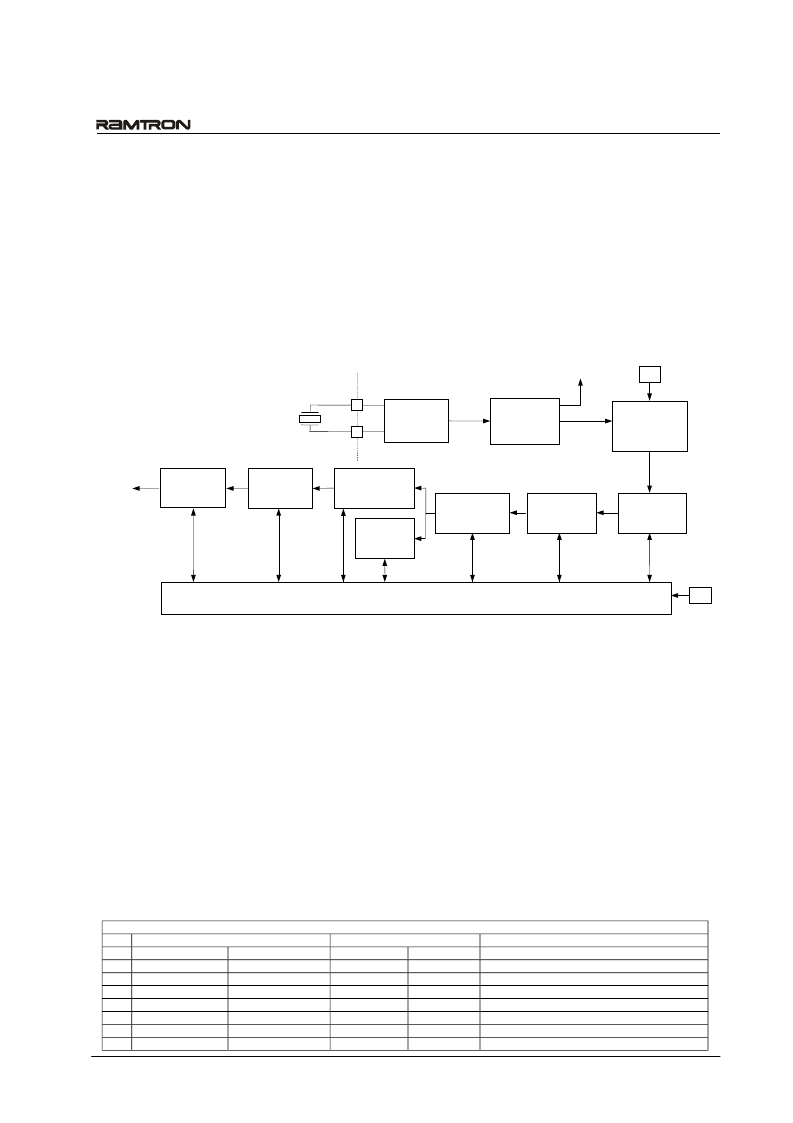

Figure 7. Real-Time Clock Core Block Diagram

Calibration

When the CAL bit in a register 00h is set to 1, the

clock enters calibration mode. In calibration mode,

the CAL/PFO output pin is dedicated to the

calibration function and the power fail output is

temporarily unavailable. Calibration operates by

applying a digital correction to the counter based on

the frequency error. In this mode, the CAL/PFO pin

is driven with a 512 Hz (nominal) square wave. Any

measured deviation from 512 Hz translates into a

timekeeping error. The user converts the measured

error in ppm and writes the appropriate correction

value to the calibration register. The correction

factors are listed in the table below. Positive ppm

errors require a negative adjustment that removes

Calibration Adjustments

Positive Calibration for slow clocks: Calibration will achieve +/- 2.17 PPM after calibration

Measured Frequency Range

Error Range (PPM)

Min

Max

Min

0

512.0000

511.9989

1

511.9989

511.9967

2.18

2

511.9967

511.9944

6.52

3

511.9944

511.9922

10.86

4

511.9922

511.9900

15.20

5

511.9900

511.9878

19.54

6

511.9878

511.9856

23.88

pulses. Negative ppm errors require a positive

correction that adds pulses. Positive ppm adjustments

have the CALS (sign) bit set to 1, where as negative

ppm adjustments have CALS = 0. After calibration,

the clock will have a maximum error of

±

2.17 ppm

or

±

0.09 minutes per month at the calibrated

temperature.

The calibration setting is stored in FRAM so is not

lost should the backup source fail. It is accessed with

bits CAL.4-0 in register 01h. This value only can be

written when the CAL bit is set to a 1. To exit the

calibration mode, the user must clear the CAL bit to a

0. When the CAL bit is 0, the CAL/PFO pin will

revert to the power fail output function.

Max

2.17

6.51

10.85

15.19

19.53

23.87

28.21

Program Calibration Register to:

000000

100001

100010

100011

100100

100101

100110

0

32.768 kHz

crystal

Oscillator

Clock

Divider

Update

Logic

512 Hz

W

R

Seconds

7 bits

Minutes

7 bits

Hours

6 bits

Date

6 bits

Months

5 bits

Years

8 bits

CF

Days

3 bits

User Interface Registers

1 Hz

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FM3204 | Integrated Processor Companion with Memory |

| FM3204-G | Integrated Processor Companion with Memory |

| FM3204-S | Integrated Processor Companion with Memory |

| FM3216 | Integrated Processor Companion with Memory |

| FM3216-G | Integrated Processor Companion with Memory |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FM3164-STR | 功能描述:監(jiān)控電路 64K w/RTC Pwr Mon WDT Bat Sw PF RoHS:否 制造商:STMicroelectronics 監(jiān)測(cè)電壓數(shù): 監(jiān)測(cè)電壓: 欠電壓閾值: 過(guò)電壓閾值: 輸出類(lèi)型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開(kāi)關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

| FM31L272 | 制造商:RAMTRON 制造商全稱(chēng):RAMTRON 功能描述:3V Integrated Processor Companion with Memory |

| FM31L272-G | 功能描述:F-RAM 4K w/RTC Pwr Mon WDT Bat Sw PF RoHS:否 存儲(chǔ)容量:512 Kbit 組織:64 K x 8 接口:SPI 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 封裝:Tube 制造商:Cypress Semiconductor |

| FM31L272-GTR | 功能描述:F-RAM 4K w/RTC Pwr Mon WDT Bat Sw PF RoHS:否 存儲(chǔ)容量:512 Kbit 組織:64 K x 8 接口:SPI 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 封裝:Tube 制造商:Cypress Semiconductor |

| FM31L274 | 制造商:RAMTRON 制造商全稱(chēng):RAMTRON 功能描述:3V Integrated Processor Companion with Memory |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。