- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375847 > FM25C160UEN (FAIRCHILD SEMICONDUCTOR CORP) SERIAL EEPROM|2KX8|CMOS|DIP|8PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號: | FM25C160UEN |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | SERIAL EEPROM|2KX8|CMOS|DIP|8PIN|PLASTIC |

| 中文描述: | 2K X 8 SPI BUS SERIAL EEPROM, PDIP8 |

| 封裝: | PLASTIC, DIP-8 |

| 文件頁數(shù): | 7/11頁 |

| 文件大小: | 102K |

| 代理商: | FM25C160UEN |

7

www.fairchildsemi.com

FM25C160U Rev. B

F

Functional Description

(Continued)

SPI communication

As mentioned before, serial communication with the EEPROM is

enabled when the /CS pin is held low and the /HOLD pin is held

high. Input data (Instruction Opcodes, Array addresses and Data)

on the SI pin is latched in on the rising edges of SCK clock signal,

starting from the first rising edge after the /CS pin goes low. During

the time the SI data is input into the EEPROM, the SO pin remains

in high impedance state. If the intended instruction is of read

nature (Array read and Status register read), then data from the

EEPROM is driven out actively on the SO pin from every falling

edge of the SCK after the last input data (SI) is latched in. During

the time the SO data is output from the EEPROM, the data on the

SI pin is ignored. Figure 2illustrates the above. Refer Figure 1 or

timing information.

HOLD function

An active communication with the EEPROM can be temporarily

suspended by bringing the /HOLD pin low when a EEPROM is

selected (/CS pin should be low) and a serial sequence with the

EEPROM is currently underway. To suspend the communication,

/HOLD pin must be driven low while SCK is low, otherwise the Hold

function will not be invoked until the next SCK high to low

transition. The EEPROM must remain selected during this se-

quence. Transitions on the SCK and SI pins are ignored during the

time the part is suspended and the SO pin will be in high

impedance state. Releasing the /HOLD pin back to high state will

allow the operation to resume from the point it was suspended.

/HOLD pin must be driven high while the SCK pin is low, otherwise

serial communication will not resume until the next SCK high to

low transition. Asserting a low on the /HOLD pin at any time will tri-

state the SO pin. Figure 3 illustrates Hold timing.

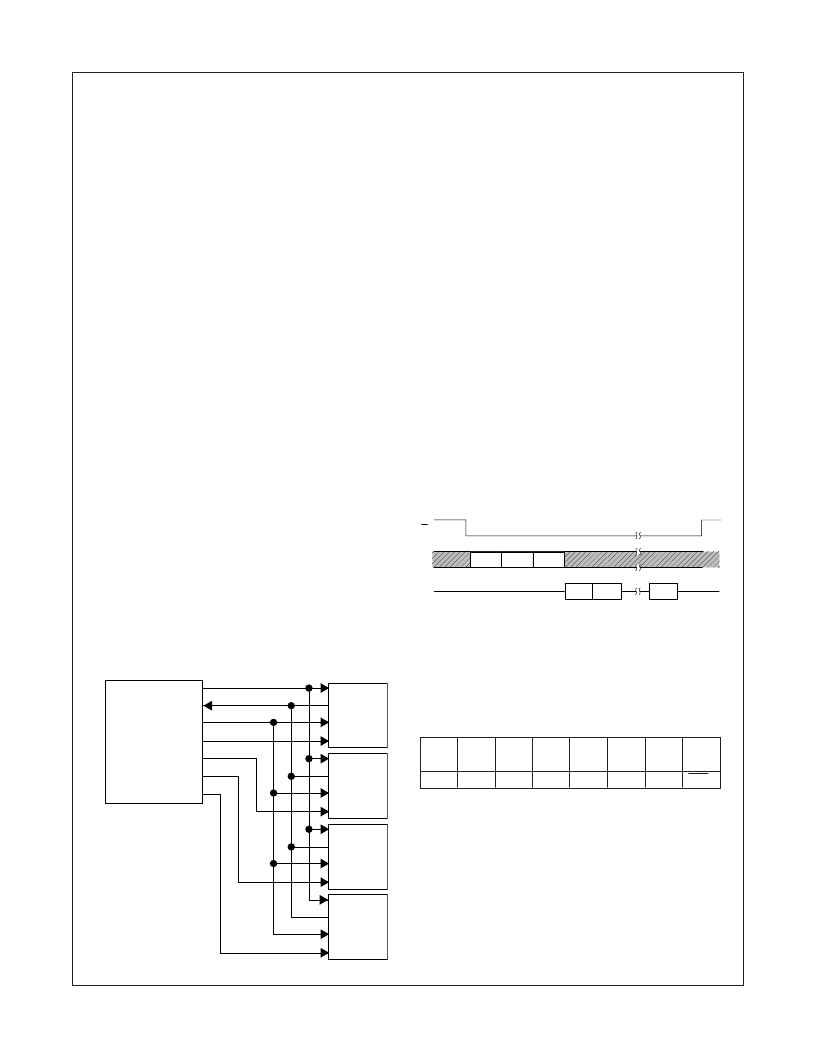

System Configuration

When multiple SPI peripherals (for e.g. EEPROMs) are present on

the bus, the SI, SO and the SCK signals can be tied together.

Figure4 illustrates a typical system configuration with respect to

/CS, SCK, SI and SO pins.

FIGURE 4. System Configuration

SI

SO

SCK

/CS

DATA OUT (MOSI)

DATA IN (MISO)

SERIAL CLOCK (SPICK)

SS0

SS1

SS2

SS3

SI

SO

SCK

/CS

SI

SO

SCK

/CS

SI

SO

SCK

/CS

SELECTION

CHIP

SPI

MASTER MCU

FM25Cxxx

SPI Modes 0 and 3 (00 and 11)

FM25C160U supports both Mode 0 and Mode 3 of operations.

The difference between Mode 0 and Mode 3 is determined by the

state of the SCK clock signal when a SPI cycle starts (when /CS

is driven low) as well as when the SPI cycle ends (when /CS is

driven high). Under Mode 0 of operation, the SCK signal is held low

both at the start and at the end of a SPI cycle. Under Mode 1 of

operation, the SCK signal is held high both at the start and at the

end of a SPI cycle. However in both of these two modes, the input

data (SI) is sampled (latched in) at the rising edge of the SCK clock

signal and the output data (SO) is driven after the falling edge of

the SCK clock signal. See Figure1 and Figure2.

READ SEQUENCE (READ)

Reading the memory via the serial SPI link requires the following

sequence. The/CS pin is pulled low to select the EEPROM. The

READ opcode is transmitted on the SI pin followed by two bytes of

address, "High byte addr" (A15-A8) and "Low byte addr" (A7-A0).

After this is done, data on the SI pin becomes don't care. The data

(D7-D0) form the address specified is then shifted out on the SO pin.

If only one byte is to be read, the /CS pin can be pulled back to the

high level. It is possible to continue the READ sequence as the byte

address is automatically incremented and data will continue to be

shifted out as clock pulses are continuously applied. When the end

of memory array is reached (last byte location), the address counter

rolls over to the start of memory array (first byte location) allowing

the entire memory to be read in one continuous READ cycle. See

Figure 5. Note that only A10-A0 address bits are treated valid by

FM25C160U while bits A15-A11 are ignored.

FIGURE 5. Read Sequence

CS

SI

SO

Read

Opcode

High Byte

Addr

Low Byte

Addr

Data

(1)

Data

(2)

Data

(n)

READ STATUS REGISTER (RDSR):

The Read Status Register (RDSR) instruction provides read

access to the status register. As mentioned before, of the 8bits of

data, only the LSB 4bits are valid and they indicate Block Protec-

tion information (BP1 and BP0), Write Enable status (WEN) and

Busy/Ready status (/RDY) of the EEPROM. MSB 4bits of are

invalid (Don

’

t cares) Following is the format of RDSR data:

TABLE 3. Status Register Format

Bit

7

X

Bit

6

X

Bit

5

X

Bit

4

X

Bit

3

BP1

Bit

2

BP0

Bit

1

WEN

Bit

0

RDY

Bit3 (BP1) and Bit2 (BP0) together indicate Block write protection

previously set on the EEPROM. Refer Table 2.

Bit1 (WEN) indicates the Write enable status of the EEPROM.

This bit is a read-only bit and is read by executing RDSR

instruction. If this bit is

“

1

”

then the EEPROM is write enabled. If

this bit is

“

0

”

then the EEPROM is write disabled.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FM25C160ULEN | SERIAL EEPROM|2KX8|CMOS|DIP|8PIN|PLASTIC |

| FM25C160ULN | SERIAL EEPROM|2KX8|CMOS|DIP|8PIN|PLASTIC |

| FM25C160ULVN | SERIAL EEPROM|2KX8|CMOS|DIP|8PIN|PLASTIC |

| FM25C160ULZEN | SERIAL EEPROM|2KX8|CMOS|DIP|8PIN|PLASTIC |

| FM25C160ULZN | SERIAL EEPROM|2KX8|CMOS|DIP|8PIN|PLASTIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FM25C160ULAA WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| FM25C160ULEM8 | 功能描述:電可擦除可編程只讀存儲器 SOIC-8 RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| FM25C160ULEM8X | 功能描述:電可擦除可編程只讀存儲器 SOIC-8 RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| FM25C160ULEN | 功能描述:電可擦除可編程只讀存儲器 DISC BY MFG 7/03 RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| FM25C160ULM8 | 功能描述:電可擦除可編程只讀存儲器 DIP-8 RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。