- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375847 > FM25C020UV (Fairchild Semiconductor Corporation) CONN-HDR,7P 1ROW,.1SP, TIN, LO PF PDF資料下載

參數(shù)資料

| 型號(hào): | FM25C020UV |

| 廠商: | Fairchild Semiconductor Corporation |

| 英文描述: | CONN-HDR,7P 1ROW,.1SP, TIN, LO PF |

| 中文描述: | 的2K位SPI⑩的CMOS EEPROM的串行接口 |

| 文件頁(yè)數(shù): | 6/11頁(yè) |

| 文件大?。?/td> | 105K |

| 代理商: | FM25C020UV |

6

www.fairchildsemi.com

FM25C020U Rev. B

F

Pin Description

Chip Select (/CS)

This is an active low input pin to the EEPROM and is generated by

a master that is controlling the EEPROM. A low level on this pin

selects the EEPROM and a high level deselects the EEPROM. All

serial communications with the EEPROM is enabled only when

this pin is held low.

Serial Clock (SCK)

This is an input pin to the EEPROM and is generated by the master

that is controlling the EEPROM. This is a clock signal that

synchronizes the communication between a master and the

EEPROM. All input information (SI) to the EEPROM is latched on

the rising edge of this clock input, while output data (SO) from the

EEPROM is driven after the falling edge of this clock input.

Serial Input (SI)

This is an input pin to the EEPROM and is generated by the master

that is controlling the EEPROM. The master transfers Input

information (Instruction Opcodes, Array addresses and Data)

serially via this pin into the EEPROM. This Input information is

latched on the rising edge of the SCK.

Serial Output (SO)

This is an output pin from the EEPROM and is used to transfer

Output data via this pin to the controlling master. Output data is

serially shifted out on this pin after the falling edge of the SCK.

Hold (/HOLD)

This is an active low input pin to the EEPROM and is generated by

the master that is controlling the EEPROM. When driven low, this

pin suspends any current communication with the EEPROM. The

suspended communication can be resumed by driving this pin

high. This feature eliminates the need to re-transmit the entire

sequence by allowing the master to resume the communication

from where it was left off. This pin should be tied high if this feature

is not used. Refer

Hold Function

description for additional

details.

Write Protect (/WP)

This is an active low input pin to the EEPROM. This pin allows

enabling and disabling of writes to memory array and status

register of the EEPROM. When this pin is held low, writes to the

memory array and status register are disabled. When this pin is

held high, writes to the memory array and status register are

enabled. Status of this pin does not affect operations other than

array write and status register write. /WP signal going low at any

time will inhibit programming, except when an internal write has

already begun. If an internal write cycle has already begun, /WP

signal going low will have no effect on the write. Refer Table1 for

Write Protection matrix.

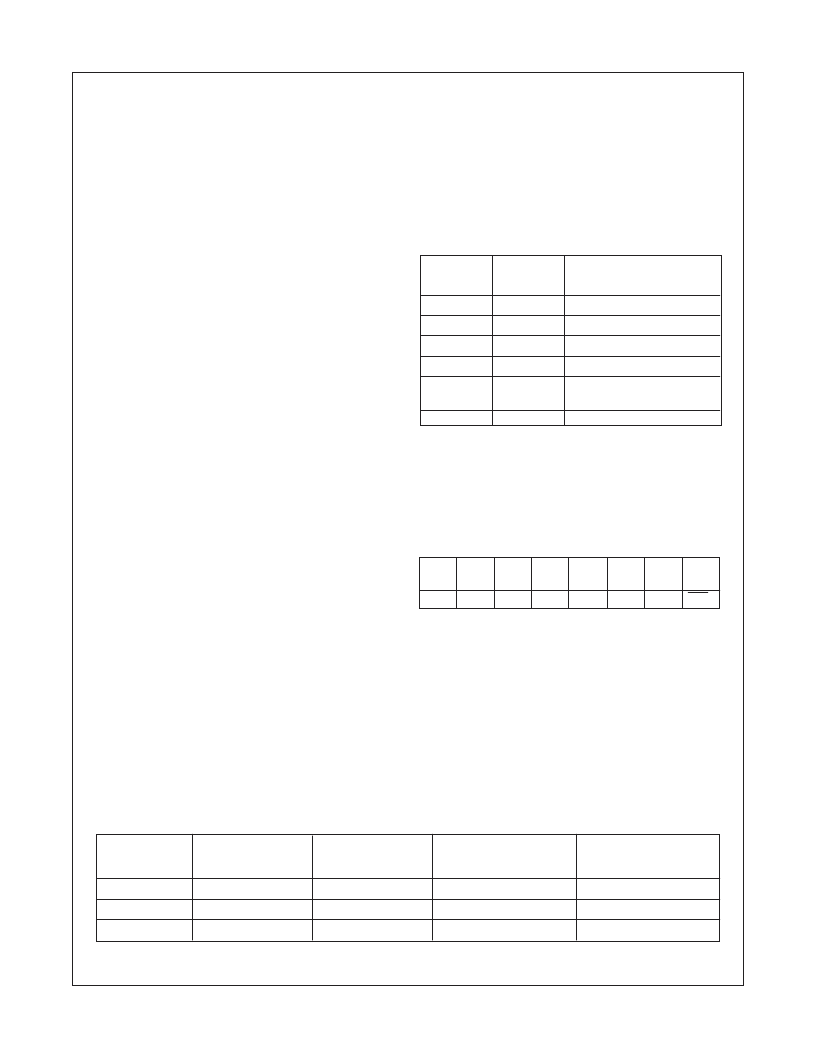

Table1. Write Protection Matrix

Functional Description

The Serial Peripheral Interface (SPI) of FM25C020U consists of

an 8-bit Instruction register to decode a specific instruction to be

executed. Six different instructions (Opcodes) are incorporated

on FM25C020U for various operations. Table2 lists the instruc-

tions set and the format for proper operation. All Opcodes, Array

addresses and Data are transferred in

“

MSB first-LSB last

”

fashion. Detailed information is provided under individual instruc-

tion descriptions.

TABLE 2. Instruction Set

Instruction Instruction

Name

Operation

Opcode

WREN

00000110

Write Enabled

WRDI

00000100

Write Disabled

RDSR

00000101

Read Status Register

WRSR

00000001

Write Status Register

READ

00000011

Read Data from Memory

Array

WRITE

00000010

Write Data to Memory Array

In addition to the Instruction register, FM25C020U also contains

an 8-bit Status register that can be accessed by RDSR and WRSR

instructions. Only the least significant (LSB) 4 bits are defined at

present and the most significant (MSB) 4 bits are undefined (don

’

t

care). The LSB 4 bits define Block Write Protection levels (BP1and

BP0), Write-enable status (WEN) and Busy/Rdy status (/RDY) of

the EEPROM.

Table 3 illustrates the format:

TABLE 3. Status Register Format

Bit

7

X

Bit

6

X

Bit

5

X

Bit

4

X

Bit

3

BP1

Bit

2

BP0

Bit

1

WEN

Bit

0

RDY

Refer RDSR and WRSR instruction descriptions for additional

information on Status register operations.

Protected Blocks

(by BP1-BP0)

/WP Pin

WEN Bit

Status Register

Unprotected Blocks

Low

X

Write Protected

Write Protected

Write Protected

High

0

Write Protected

Write Protected

Write Protected

High

1

Write Allowed

Write Protected

Write Allowed

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FM25C040 | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| FM25C040U | LOW PROFILE .025 SQ STRIPS |

| FM25C040UE | CONN,HEADER,2X8,AV,.100 |

| FM25C040UV | CONNECTOR,HDR,DUAL,10PIN |

| FM25C040UEM8 | SERIAL EEPROM|512X8|CMOS|SOP|8PIN|PLASTIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FM25C020UVM8 | 功能描述:電可擦除可編程只讀存儲(chǔ)器 SOIC-8 RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| FM25C020UVM8X | 功能描述:電可擦除可編程只讀存儲(chǔ)器 DISC BY MFG 7/03 RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| FM25C020UVMT8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SPI Serial EEPROM |

| FM25C020UVN | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SPI Serial EEPROM |

| FM25C040 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:4K-Bit SPI⑩ Interface Serial CMOS EEPROM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。