- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375726 > FAN6520AIMX (FAIRCHILD SEMICONDUCTOR CORP) Single Synchronous Buck PWM Controller PDF資料下載

參數(shù)資料

| 型號: | FAN6520AIMX |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 穩(wěn)壓器 |

| 英文描述: | Single Synchronous Buck PWM Controller |

| 中文描述: | 1 A SWITCHING CONTROLLER, 340 kHz SWITCHING FREQ-MAX, PDSO8 |

| 封裝: | MS-012AA, SOIC-8 |

| 文件頁數(shù): | 11/15頁 |

| 文件大小: | 580K |

| 代理商: | FAN6520AIMX |

PRODUCT SPECIFICATION

FAN6520A

REV. 1.0.2 8/26/04

11

Power MOSFET Selection

For more information on MOSFET selection for synchro-

nous buck regulators, refer to:

AN-6005: Synchronous Buck

MOSFET Loss Calculations.

This Fairchild app note is located at:

http://www.fairchildsemi.com/an/AN/AN-6005.pdf

Losses in a MOSFET are the sum of its switching (P

SW

) and

conduction (P

COND

) losses.

In typical applications, the FAN6520A converter's output

voltage is low with respect to its input voltage, therefore the

lower MOSFET (Q2) is conducting the full load current for

most of the cycle. Therefore choose a MOSFET for Q2

which has low R

DS(ON)

to minimize conduction losses.

In contrast, the high-side MOSFET (Q1) has a much shorter

duty cycle, and its conduction loss will therefore have less of

an impact. Q1, however, sees most of the switching losses,

so Q1’s primary selection criteria should be gate charge.

High-Side Losses

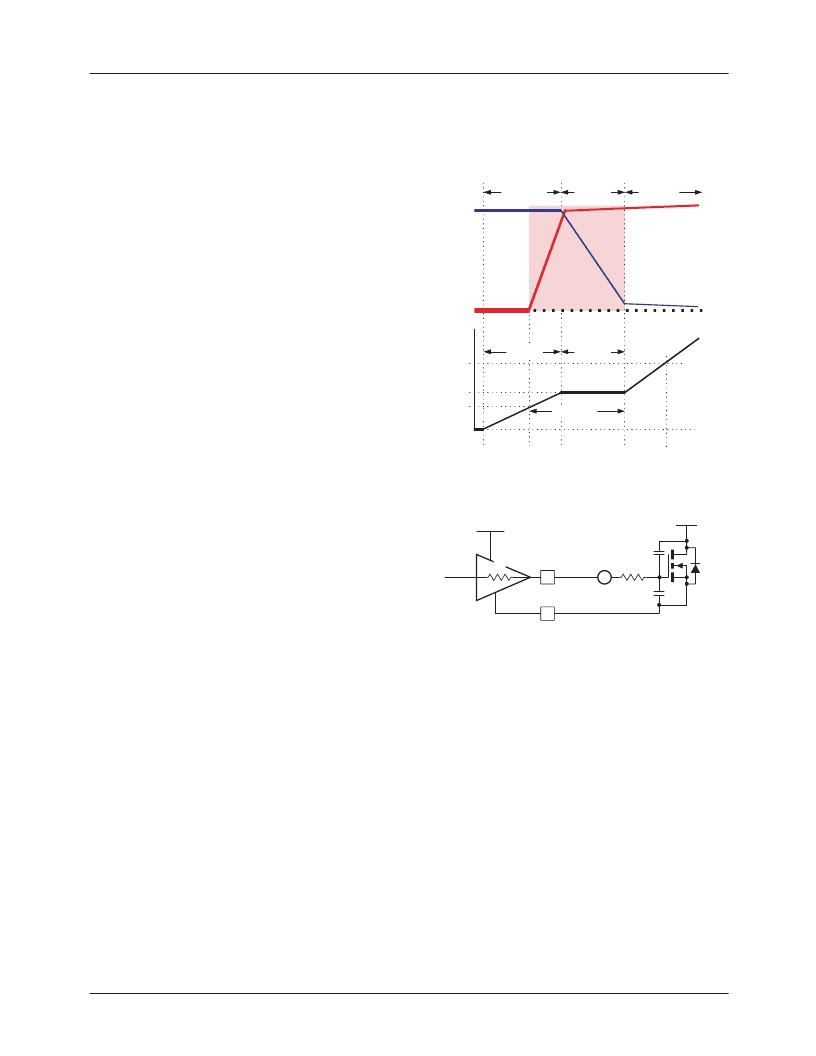

Figure 10 shows a MOSFET’s switching interval, with the

upper graph being the voltage and current on the Drain to

Source and the lower graph detailing V

GS

vs. time with a

constant current charging the gate. The x-axis, therefore, is

also representative of gate charge (Q

G

) . C

ISS

= C

GD

+ C

GS

,

and it controls t1, t2, and t4 timing. C

GD

receives the current

from the gate driver during t3 (as V

DS

is falling). The gate

charge (Q

G

) parameters on the lower graph are either

specified or can be derived from the MOSFET’s datasheet.

Assuming switching losses are about the same for both the

rising edge and falling edge, Q1’s switching losses, occur

during the shaded time when the MOSFET has voltage

across it and current through it.

These losses are given by:

P

UPPER

= P

SW

+ P

COND

where:

P

UPPER

is the upper MOSFET’s total losses, and P

SW

and

P

COND

are the switching and conduction losses for a given

MOSFET. R

DS(ON)

is at the maximum junction temperature

(T

J

). t

S

is the switching period (rise or fall time) and is t2+t3

(Figure 10).

The driver’s impedance and C

ISS

determine t2 while t3’s

period is controlled by the driver’s impedance and Q

GD

.

Since most of t

S

occurs when V

GS

= V

SP

we can use a

constant current assumption for the driver to simplify the

calculation of t

S

:

Figure 10. Switching Losses and Q

G

Figure 11. Drive Equivalent Circuit

Most MOSFET vendors specify Q

GD

and Q

GS

. Q

G(SW)

can

be determined as: Q

G(SW)

= Q

GD

+ Q

GS

– Q

TH

where Q

TH

is

the gate charge required to get the MOSFET to its threshold

(V

TH

). For the high-side MOSFET, V

DS

= V

IN

, which can be

as high as 20V in a typical portable application. Care should

also be taken to include the delivery of the MOSFET’s gate

power (P

GATE

) in calculating the power dissipation required

for the FAN6520A:

P

GATE

= Q

G

×

VCC

×

F

SW

(17)

where Q

G

is the total gate charge to reach VCC.

P

SW

V

--------2

I

L

×

2

×

t

s

×

F

SW

=

(14)

P

COND

V

IN

---V

I

OUT

2

×

R

DS ON

)

×

=

(15)

V

SP

V

TH

V

GS

t1

t2

t3

4.5V

t4

t5

Q

G(SW)

V

DS

I

D

Q

GS

Q

GD

C

ISS

C

GD

C

ISS

C

GD

R

D

R

GATE

C

GS

HDRV

5V

SW

VIN

G

t

s

Q

DRIVER

)

I

Q

DRIVER

)

V

SP

R

GATE

+

–

R

------------VCC

≈

≈

(16)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FAN6520AM | Single Synchronous Buck PWM Controller |

| FAN6520AMX | Single Synchronous Buck PWM Controller |

| FAN6550M | |

| FAN6550MX | |

| FAN6550 | 2A DDR Bus Termination Regulator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FAN6520AM | 功能描述:電壓模式 PWM 控制器 Single Synchronous Buck PWM Controller RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:1 拓?fù)浣Y(jié)構(gòu):Buck 輸出電壓:34 V 輸出電流: 開關(guān)頻率: 工作電源電壓:4.5 V to 5.5 V 電源電流:600 uA 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝 / 箱體:WSON-8 封裝:Reel |

| FAN6520AM_Q | 功能描述:電壓模式 PWM 控制器 Single Synchronous Buck PWM Controller RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:1 拓?fù)浣Y(jié)構(gòu):Buck 輸出電壓:34 V 輸出電流: 開關(guān)頻率: 工作電源電壓:4.5 V to 5.5 V 電源電流:600 uA 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝 / 箱體:WSON-8 封裝:Reel |

| FAN6520AMX | 功能描述:電壓模式 PWM 控制器 Single Synchronous Buck PWM Controller RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:1 拓?fù)浣Y(jié)構(gòu):Buck 輸出電壓:34 V 輸出電流: 開關(guān)頻率: 工作電源電壓:4.5 V to 5.5 V 電源電流:600 uA 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝 / 箱體:WSON-8 封裝:Reel |

| FAN6520AMX_Q | 功能描述:電壓模式 PWM 控制器 Single Synchronous Buck PWM Controller RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:1 拓?fù)浣Y(jié)構(gòu):Buck 輸出電壓:34 V 輸出電流: 開關(guān)頻率: 工作電源電壓:4.5 V to 5.5 V 電源電流:600 uA 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝 / 箱體:WSON-8 封裝:Reel |

| FAN6520AMXCT | 制造商:Fairchild Semiconductor Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。