- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4404 > EP4CGX75CF23C7 (Altera)IC CYCLONE IV GX FPGA 75K 484FBG PDF資料下載

參數(shù)資料

| 型號: | EP4CGX75CF23C7 |

| 廠商: | Altera |

| 文件頁數(shù): | 21/42頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC CYCLONE IV GX FPGA 75K 484FBG |

| 產(chǎn)品培訓(xùn)模塊: | Cyclone IV FPGA Family Overview |

| 特色產(chǎn)品: | Cyclone? IV FPGAs |

| 標(biāo)準(zhǔn)包裝: | 60 |

| 系列: | CYCLONE® IV GX |

| LAB/CLB數(shù): | 4620 |

| 邏輯元件/單元數(shù): | 73920 |

| RAM 位總計(jì): | 4257792 |

| 輸入/輸出數(shù): | 290 |

| 電源電壓: | 1.16 V ~ 1.24 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 484-BGA |

| 供應(yīng)商設(shè)備封裝: | 484-FBGA(23x23) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

1–28

Chapter 1: Cyclone IV Device Datasheet

Switching Characteristics

December 2013

Altera Corporation

f For more information about the supported maximum clock rate, device and pin

planning, IP implementation, and device termination, refer to Section III: System

Performance Specifications of the External Memory Interfaces Handbook.

1 Actual achievable frequency depends on design- and system-specific factors. Perform

HSPICE/IBIS simulations based on your specific design and system setup to

determine the maximum achievable frequency in your system.

High-Speed I/O Specifications

Table 1–31 through Table 1–36 list the high-speed I/O timing for Cyclone IV devices.

For definitions of high-speed timing specifications, refer to “Glossary” on page 1–37.

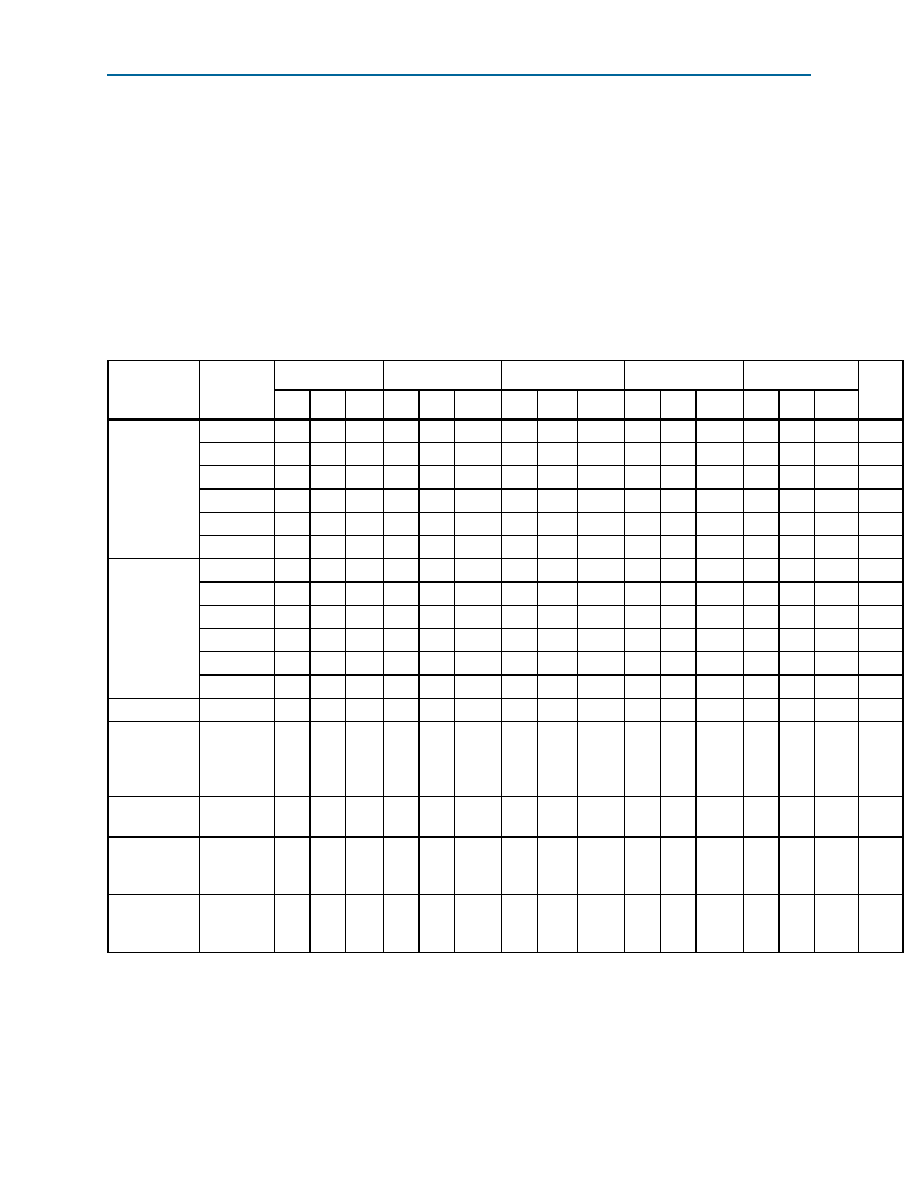

Table 1–31. RSDS Transmitter Timing Specifications for Cyclone IV Devices (1), (2), (4) (Part 1 of 2)

Symbol

Modes

C6

C7, I7

C8, A7

C8L, I8L

C9L

Unit

Min

Typ

Max Min

Typ

Max

Min

Typ

Max

Min

Typ

Max

Min

Typ

Max

fHSCLK

(input clock

frequency)

×10

5

—

180

5

—

155.5

5

—

155.5

5

—

155.5

5

—

132.5

MHz

×8

5

—

180

5

—

155.5

5

—

155.5

5

—

155.5

5

—

132.5

MHz

×7

5

—

180

5

—

155.5

5

—

155.5

5

—

155.5

5

—

132.5

MHz

×4

5

—

180

5

—

155.5

5

—

155.5

5

—

155.5

5

—

132.5

MHz

×2

5

—

180

5

—

155.5

5

—

155.5

5

—

155.5

5

—

132.5

MHz

×1

5

—

360

5

—

311

5

—

311

5

—

311

5

—

265

MHz

Device

operation in

Mbps

×10

100

—

360

100

—

311

100

—

311

100

—

311

100

—

265

Mbps

×8

80

—

360

80

—

311

80

—

311

80

—

311

80

—

265

Mbps

×7

70

—

360

70

—

311

70

—

311

70

—

311

70

—

265

Mbps

×4

40

—

360

40

—

311

40

—

311

40

—

311

40

—

265

Mbps

×2

20

—

360

20

—

311

20

—

311

20

—

311

20

—

265

Mbps

×1

10

—

360

10

—

311

10

—

311

10

—

311

10

—

265

Mbps

tDUTY

—

45

—

55

45

—

55

45

—

55

45

—

55

45

—

55

%

Transmitter

channel-to-

channel skew

(TCCS)

—

200

—

200

—

200

—

200

—

200

ps

Output jitter

(peak to peak)

—

500

—

500

—

550

—

600

—

700

ps

tRISE

20 – 80%,

CLOAD =

5pF

—

500

—

500

—

500

—

500

—

500

—

ps

tFALL

20 – 80%,

CLOAD =

5pF

—

500

—

500

—

500

—

500

—

500

—

ps

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AMM25DTKN | CONN EDGECARD 50POS DIP .156 SLD |

| AMM25DTKH | CONN EDGECARD 50POS DIP .156 SLD |

| AMM25DTKD | CONN EDGECARD 50POS DIP .156 SLD |

| ACC49DRES-S734 | CONN EDGECARD 98POS .100 EYELET |

| ABC49DRES-S734 | CONN EDGECARD 98POS .100 EYELET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP4CGX75CF23C7N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone IV GX 4620 LABs 290 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CGX75CF23C8 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone IV GX 4620 LABs 290 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CGX75CF23C8N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone IV GX 4620 LABs 290 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CGX75CF23I7 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone IV GX 4620 LABs 290 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CGX75CF23I7N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone IV GX 4620 LABs 290 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。