- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄4412 > EP4CE75F23C8N (Altera)IC CYCLONE IV FPGA 75K 484FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | EP4CE75F23C8N |

| 廠商: | Altera |

| 文件頁(yè)數(shù): | 36/42頁(yè) |

| 文件大小: | 0K |

| 描述: | IC CYCLONE IV FPGA 75K 484FBGA |

| 產(chǎn)品培訓(xùn)模塊: | Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview |

| 特色產(chǎn)品: | Cyclone? IV FPGAs |

| 標(biāo)準(zhǔn)包裝: | 60 |

| 系列: | CYCLONE® IV E |

| LAB/CLB數(shù): | 4713 |

| 邏輯元件/單元數(shù): | 75408 |

| RAM 位總計(jì): | 2810880 |

| 輸入/輸出數(shù): | 292 |

| 電源電壓: | 1.15 V ~ 1.25 V |

| 安裝類(lèi)型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 484-BGA |

| 供應(yīng)商設(shè)備封裝: | 484-FBGA(23x23) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)當(dāng)前第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)

Chapter 1: Cyclone IV Device Datasheet

1–41

Glossary

December 2013

Altera Corporation

V

VCM(DC)

DC common mode input voltage.

VDIF(AC)

AC differential input voltage: The minimum AC input differential voltage required for switching.

VDIF(DC)

DC differential input voltage: The minimum DC input differential voltage required for switching.

VICM

Input common mode voltage: The common mode of the differential signal at the receiver.

VID

Input differential voltage swing: The difference in voltage between the positive and

complementary conductors of a differential transmission at the receiver.

VIH

Voltage input high: The minimum positive voltage applied to the input that is accepted by the

device as a logic high.

VIH(AC)

High-level AC input voltage.

VIH(DC)

High-level DC input voltage.

VIL

Voltage input low: The maximum positive voltage applied to the input that is accepted by the

device as a logic low.

VIL (AC)

Low-level AC input voltage.

VIL (DC)

Low-level DC input voltage.

VIN

DC input voltage.

VOCM

Output common mode voltage: The common mode of the differential signal at the transmitter.

VOD

Output differential voltage swing: The difference in voltage between the positive and

complementary conductors of a differential transmission at the transmitter. VOD = VOH – VOL.

VOH

Voltage output high: The maximum positive voltage from an output that the device considers is

accepted as the minimum positive high level.

VOL

Voltage output low: The maximum positive voltage from an output that the device considers is

accepted as the maximum positive low level.

VOS

Output offset voltage: VOS = (VOH + VOL) / 2.

VOX (AC)

AC differential output cross point voltage: the voltage at which the differential output signals

must cross.

VREF

Reference voltage for the SSTL and HSTL I/O standards.

VREF (AC)

AC input reference voltage for the SSTL and HSTL I/O standards. VREF(AC) = VREF(DC) + noise. The

peak-to-peak AC noise on VREF must not exceed 2% of VREF(DC).

VREF (DC)

DC input reference voltage for the SSTL and HSTL I/O standards.

VSWING (AC)

AC differential input voltage: AC input differential voltage required for switching. For the SSTL

differential I/O standard, refer to Input Waveforms.

VSWING (DC)

DC differential input voltage: DC input differential voltage required for switching. For the SSTL

differential I/O standard, refer to Input Waveforms.

VTT

Termination voltage for the SSTL and HSTL I/O standards.

VX (AC)

AC differential input cross point voltage: The voltage at which the differential input signals must

cross.

W

——

X

——

Y

——

Z

——

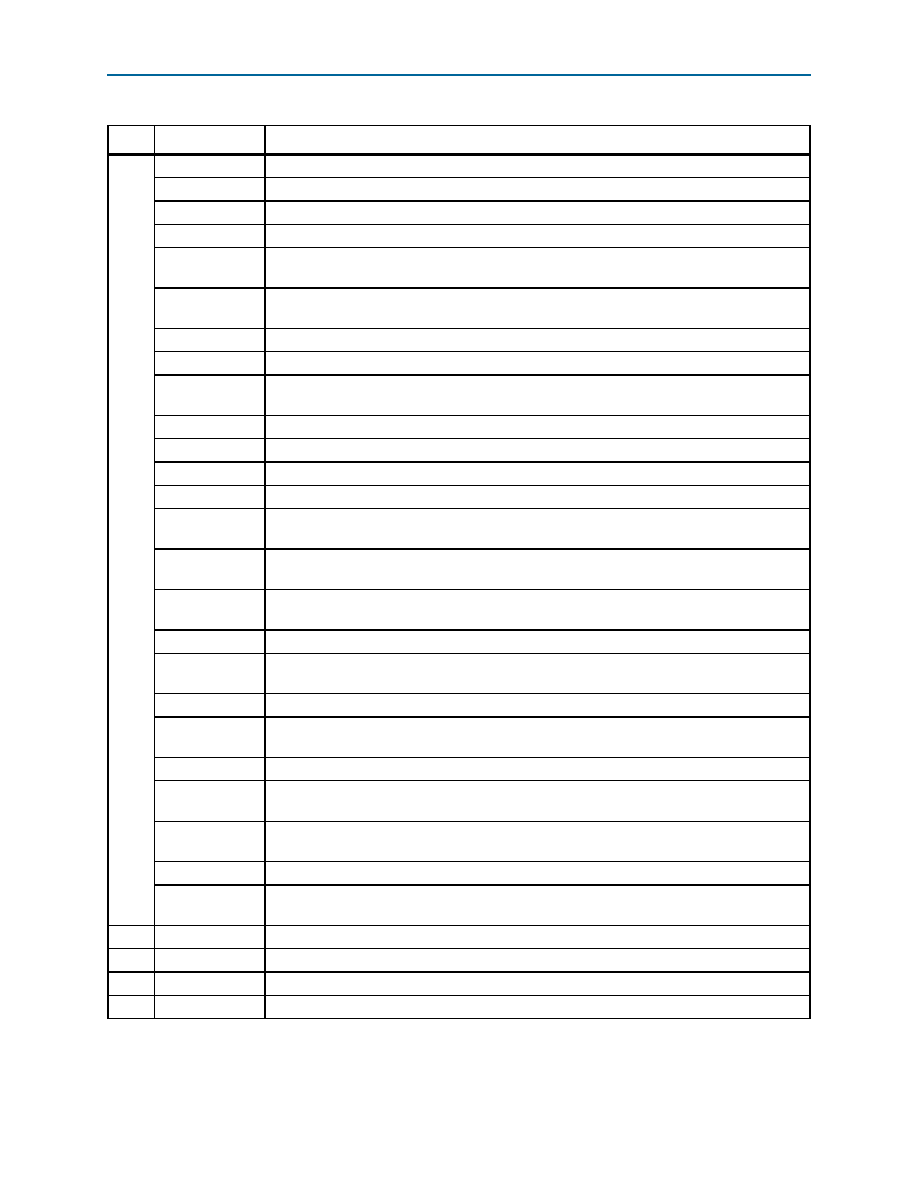

Table 1–46. Glossary (Part 5 of 5)

Letter

Term

Definitions

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M1AGL1000V5-FGG256I | IC FPGA 1KB FLASH 1M 256-FBGA |

| M1AGL1000V5-FG256I | IC FPGA 1KB FLASH 1M 256-FBGA |

| AGL1000V5-FG256I | IC FPGA 1KB FLASH 1M 256FBGA |

| AGL1000V5-FGG256I | IC FPGA 1KB FLASH 1M 256FBGA |

| BR93L86RFJ-WE2 | IC EEPROM 16KBIT 2MHZ 8SOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP4CE75F23C9L | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 FPGA - Cyclone IV E 4713 LABs 292 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CE75F23C9LN | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 FPGA - Cyclone IV E 4713 LABs 292 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CE75F23I7 | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 FPGA - Cyclone IV E 4713 LABs 292 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CE75F23I7N | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 FPGA - Cyclone IV E 4713 LABs 292 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CE75F23I8L | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 FPGA - Cyclone IV E 4713 LABs 292 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。