- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4326 > EP2S90F1020I4 (Altera)IC STRATIX II FPGA 90K 1020-FBGA PDF資料下載

參數(shù)資料

| 型號: | EP2S90F1020I4 |

| 廠商: | Altera |

| 文件頁數(shù): | 420/768頁 |

| 文件大小: | 0K |

| 描述: | IC STRATIX II FPGA 90K 1020-FBGA |

| 產(chǎn)品培訓(xùn)模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 標(biāo)準(zhǔn)包裝: | 6 |

| 系列: | Stratix® II |

| LAB/CLB數(shù): | 4548 |

| 邏輯元件/單元數(shù): | 90960 |

| RAM 位總計(jì): | 4520488 |

| 輸入/輸出數(shù): | 758 |

| 電源電壓: | 1.15 V ~ 1.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 1020-BBGA |

| 供應(yīng)商設(shè)備封裝: | 1020-FBGA(33x33) |

| 其它名稱: | 544-1919 EP2S90F1020I4-ND |

Altera Corporation

4–39

January 2008

Stratix II Device Handbook, Volume 2

Selectable I/O Standards in Stratix II and Stratix II GX Devices

single-ended outputs must be placed at least one LAB row away from the

differential I/O pins. There are no restrictions on the placement of

single-ended input pins with respect to differential I/O pins.

Single-ended input pins may be placed within the same LAB row as

differential I/O pins. However, the single-ended input’s IOE register is

not available. The input must be implemented within the core logic.

This single-ended output pin placement restriction only applies when

using the LVDS or HyperTransport I/O standards in the left and right

I/O banks. There are no restrictions for single-ended output pin

placement with respect to differential clock pins in the top and bottom

I/O banks.

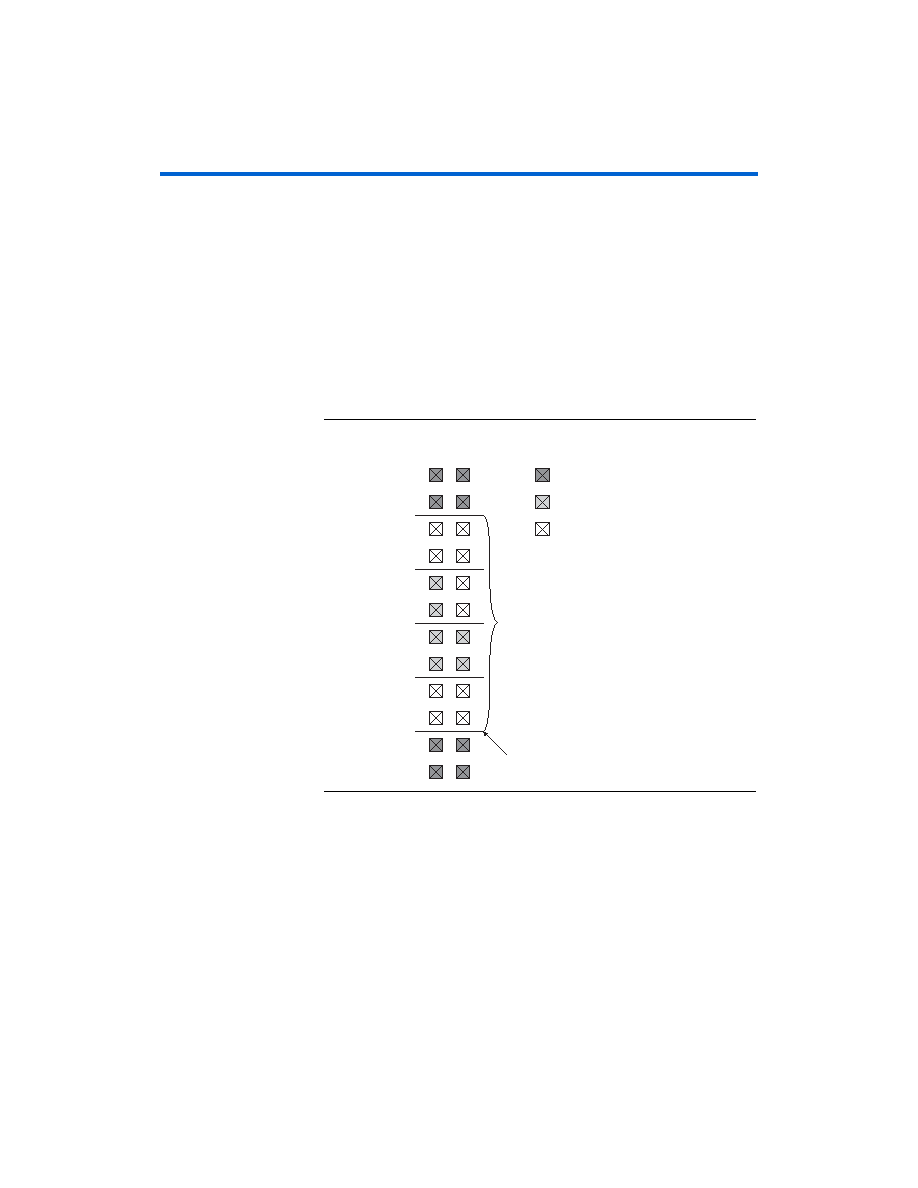

Figure 4–25. Single-Ended Output Pin Placement with Respect to Differential

I/O Pins

DC Guidelines

Power budgets are essential to ensure the reliability and functionality of

a system application. You are often required to perform power

dissipation analysis on each device in the system to come out with the

total power dissipated in that system, which is composed of a static

component and a dynamic component.

The static power consumption of a device is the total DC current flowing

from VCCIO to ground.

Single-Ended Output Pin

Differential I/O Pin

Single_Ended Input

Single-Ended Outputs

Not Allowed

Row Boundary

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 180-062-271L000 | CONN DB62 FMALE HD CRIMP Y-CHROM |

| 180-062-171L030 | CONN DB62 MALE HD CRIMP Y-CHROM |

| 180-062-171L020 | CONN DB62 MALE HD CRIMP Y-CHROM |

| 170-015-271L020 | CONN DB15 CRIMP FEM YLW CHROME |

| 24LC01BHT-E/LT | IC EEPROM 1KBIT 400KHZ SC70-5 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP2S90F1020I4N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix II 4548 LABs 758 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP2S90F1508C3 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix II 4548 LABs 902 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP2S90F1508C3ES | 制造商:ALTERA 制造商全稱:Altera Corporation 功能描述:Stratix II Device Family Data Sheet |

| EP2S90F1508C3N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix II 4548 LABs 902 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP2S90F1508C4 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix II 4548 LABs 902 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。