- 鎮ㄧ従鍦ㄧ殑浣嶇疆锛�璨疯常IC缍� > PDF鐩寗4355 > EP2S30F672C3 (Altera)IC STRATIX II FPGA 30K 672-FBGA PDF璩囨枡涓嬭級

鍙冩暩璩囨枡

| 鍨嬭櫉锛� | EP2S30F672C3 |

| 寤犲晢锛� | Altera |

| 鏂囦欢闋佹暩锛� | 38/768闋� |

| 鏂囦欢澶у皬锛� | 0K |

| 鎻忚堪锛� | IC STRATIX II FPGA 30K 672-FBGA |

| 鐢㈠搧鍩硅〒妯″锛� | Three Reasons to Use FPGA's in Industrial Designs |

| 妯欐簴鍖呰锛� | 10 |

| 绯诲垪锛� | Stratix® II |

| LAB/CLB鏁革細 | 1694 |

| 閭忚集鍏冧欢/鍠厓鏁革細 | 33880 |

| RAM 浣嶇附瑷堬細 | 1369728 |

| 杓稿叆/杓稿嚭鏁革細 | 500 |

| 闆绘簮闆诲锛� | 1.15 V ~ 1.25 V |

| 瀹夎椤炲瀷锛� | 琛ㄩ潰璨艰 |

| 宸ヤ綔婧害锛� | 0°C ~ 85°C |

| 灏佽/澶栨锛� | 672-BBGA |

| 渚涙噳鍟嗚ō鍌欏皝瑁濓細 | 672-BGA锛�27x27锛� |

| 鍏跺畠鍚嶇ū锛� | 544-1895 EP2S30F672C3-ND |

绗�1闋�绗�2闋�绗�3闋�绗�4闋�绗�5闋�绗�6闋�绗�7闋�绗�8闋�绗�9闋�绗�10闋�绗�11闋�绗�12闋�绗�13闋�绗�14闋�绗�15闋�绗�16闋�绗�17闋�绗�18闋�绗�19闋�绗�20闋�绗�21闋�绗�22闋�绗�23闋�绗�24闋�绗�25闋�绗�26闋�绗�27闋�绗�28闋�绗�29闋�绗�30闋�绗�31闋�绗�32闋�绗�33闋�绗�34闋�绗�35闋�绗�36闋�绗�37闋�鐣跺墠绗�38闋�绗�39闋�绗�40闋�绗�41闋�绗�42闋�绗�43闋�绗�44闋�绗�45闋�绗�46闋�绗�47闋�绗�48闋�绗�49闋�绗�50闋�绗�51闋�绗�52闋�绗�53闋�绗�54闋�绗�55闋�绗�56闋�绗�57闋�绗�58闋�绗�59闋�绗�60闋�绗�61闋�绗�62闋�绗�63闋�绗�64闋�绗�65闋�绗�66闋�绗�67闋�绗�68闋�绗�69闋�绗�70闋�绗�71闋�绗�72闋�绗�73闋�绗�74闋�绗�75闋�绗�76闋�绗�77闋�绗�78闋�绗�79闋�绗�80闋�绗�81闋�绗�82闋�绗�83闋�绗�84闋�绗�85闋�绗�86闋�绗�87闋�绗�88闋�绗�89闋�绗�90闋�绗�91闋�绗�92闋�绗�93闋�绗�94闋�绗�95闋�绗�96闋�绗�97闋�绗�98闋�绗�99闋�绗�100闋�绗�101闋�绗�102闋�绗�103闋�绗�104闋�绗�105闋�绗�106闋�绗�107闋�绗�108闋�绗�109闋�绗�110闋�绗�111闋�绗�112闋�绗�113闋�绗�114闋�绗�115闋�绗�116闋�绗�117闋�绗�118闋�绗�119闋�绗�120闋�绗�121闋�绗�122闋�绗�123闋�绗�124闋�绗�125闋�绗�126闋�绗�127闋�绗�128闋�绗�129闋�绗�130闋�绗�131闋�绗�132闋�绗�133闋�绗�134闋�绗�135闋�绗�136闋�绗�137闋�绗�138闋�绗�139闋�绗�140闋�绗�141闋�绗�142闋�绗�143闋�绗�144闋�绗�145闋�绗�146闋�绗�147闋�绗�148闋�绗�149闋�绗�150闋�绗�151闋�绗�152闋�绗�153闋�绗�154闋�绗�155闋�绗�156闋�绗�157闋�绗�158闋�绗�159闋�绗�160闋�绗�161闋�绗�162闋�绗�163闋�绗�164闋�绗�165闋�绗�166闋�绗�167闋�绗�168闋�绗�169闋�绗�170闋�绗�171闋�绗�172闋�绗�173闋�绗�174闋�绗�175闋�绗�176闋�绗�177闋�绗�178闋�绗�179闋�绗�180闋�绗�181闋�绗�182闋�绗�183闋�绗�184闋�绗�185闋�绗�186闋�绗�187闋�绗�188闋�绗�189闋�绗�190闋�绗�191闋�绗�192闋�绗�193闋�绗�194闋�绗�195闋�绗�196闋�绗�197闋�绗�198闋�绗�199闋�绗�200闋�绗�201闋�绗�202闋�绗�203闋�绗�204闋�绗�205闋�绗�206闋�绗�207闋�绗�208闋�绗�209闋�绗�210闋�绗�211闋�绗�212闋�绗�213闋�绗�214闋�绗�215闋�绗�216闋�绗�217闋�绗�218闋�绗�219闋�绗�220闋�绗�221闋�绗�222闋�绗�223闋�绗�224闋�绗�225闋�绗�226闋�绗�227闋�绗�228闋�绗�229闋�绗�230闋�绗�231闋�绗�232闋�绗�233闋�绗�234闋�绗�235闋�绗�236闋�绗�237闋�绗�238闋�绗�239闋�绗�240闋�绗�241闋�绗�242闋�绗�243闋�绗�244闋�绗�245闋�绗�246闋�绗�247闋�绗�248闋�绗�249闋�绗�250闋�绗�251闋�绗�252闋�绗�253闋�绗�254闋�绗�255闋�绗�256闋�绗�257闋�绗�258闋�绗�259闋�绗�260闋�绗�261闋�绗�262闋�绗�263闋�绗�264闋�绗�265闋�绗�266闋�绗�267闋�绗�268闋�绗�269闋�绗�270闋�绗�271闋�绗�272闋�绗�273闋�绗�274闋�绗�275闋�绗�276闋�绗�277闋�绗�278闋�绗�279闋�绗�280闋�绗�281闋�绗�282闋�绗�283闋�绗�284闋�绗�285闋�绗�286闋�绗�287闋�绗�288闋�绗�289闋�绗�290闋�绗�291闋�绗�292闋�绗�293闋�绗�294闋�绗�295闋�绗�296闋�绗�297闋�绗�298闋�绗�299闋�绗�300闋�绗�301闋�绗�302闋�绗�303闋�绗�304闋�绗�305闋�绗�306闋�绗�307闋�绗�308闋�绗�309闋�绗�310闋�绗�311闋�绗�312闋�绗�313闋�绗�314闋�绗�315闋�绗�316闋�绗�317闋�绗�318闋�绗�319闋�绗�320闋�绗�321闋�绗�322闋�绗�323闋�绗�324闋�绗�325闋�绗�326闋�绗�327闋�绗�328闋�绗�329闋�绗�330闋�绗�331闋�绗�332闋�绗�333闋�绗�334闋�绗�335闋�绗�336闋�绗�337闋�绗�338闋�绗�339闋�绗�340闋�绗�341闋�绗�342闋�绗�343闋�绗�344闋�绗�345闋�绗�346闋�绗�347闋�绗�348闋�绗�349闋�绗�350闋�绗�351闋�绗�352闋�绗�353闋�绗�354闋�绗�355闋�绗�356闋�绗�357闋�绗�358闋�绗�359闋�绗�360闋�绗�361闋�绗�362闋�绗�363闋�绗�364闋�绗�365闋�绗�366闋�绗�367闋�绗�368闋�绗�369闋�绗�370闋�绗�371闋�绗�372闋�绗�373闋�绗�374闋�绗�375闋�绗�376闋�绗�377闋�绗�378闋�绗�379闋�绗�380闋�绗�381闋�绗�382闋�绗�383闋�绗�384闋�绗�385闋�绗�386闋�绗�387闋�绗�388闋�绗�389闋�绗�390闋�绗�391闋�绗�392闋�绗�393闋�绗�394闋�绗�395闋�绗�396闋�绗�397闋�绗�398闋�绗�399闋�绗�400闋�绗�401闋�绗�402闋�绗�403闋�绗�404闋�绗�405闋�绗�406闋�绗�407闋�绗�408闋�绗�409闋�绗�410闋�绗�411闋�绗�412闋�绗�413闋�绗�414闋�绗�415闋�绗�416闋�绗�417闋�绗�418闋�绗�419闋�绗�420闋�绗�421闋�绗�422闋�绗�423闋�绗�424闋�绗�425闋�绗�426闋�绗�427闋�绗�428闋�绗�429闋�绗�430闋�绗�431闋�绗�432闋�绗�433闋�绗�434闋�绗�435闋�绗�436闋�绗�437闋�绗�438闋�绗�439闋�绗�440闋�绗�441闋�绗�442闋�绗�443闋�绗�444闋�绗�445闋�绗�446闋�绗�447闋�绗�448闋�绗�449闋�绗�450闋�绗�451闋�绗�452闋�绗�453闋�绗�454闋�绗�455闋�绗�456闋�绗�457闋�绗�458闋�绗�459闋�绗�460闋�绗�461闋�绗�462闋�绗�463闋�绗�464闋�绗�465闋�绗�466闋�绗�467闋�绗�468闋�绗�469闋�绗�470闋�绗�471闋�绗�472闋�绗�473闋�绗�474闋�绗�475闋�绗�476闋�绗�477闋�绗�478闋�绗�479闋�绗�480闋�绗�481闋�绗�482闋�绗�483闋�绗�484闋�绗�485闋�绗�486闋�绗�487闋�绗�488闋�绗�489闋�绗�490闋�绗�491闋�绗�492闋�绗�493闋�绗�494闋�绗�495闋�绗�496闋�绗�497闋�绗�498闋�绗�499闋�绗�500闋�绗�501闋�绗�502闋�绗�503闋�绗�504闋�绗�505闋�绗�506闋�绗�507闋�绗�508闋�绗�509闋�绗�510闋�绗�511闋�绗�512闋�绗�513闋�绗�514闋�绗�515闋�绗�516闋�绗�517闋�绗�518闋�绗�519闋�绗�520闋�绗�521闋�绗�522闋�绗�523闋�绗�524闋�绗�525闋�绗�526闋�绗�527闋�绗�528闋�绗�529闋�绗�530闋�绗�531闋�绗�532闋�绗�533闋�绗�534闋�绗�535闋�绗�536闋�绗�537闋�绗�538闋�绗�539闋�绗�540闋�绗�541闋�绗�542闋�绗�543闋�绗�544闋�绗�545闋�绗�546闋�绗�547闋�绗�548闋�绗�549闋�绗�550闋�绗�551闋�绗�552闋�绗�553闋�绗�554闋�绗�555闋�绗�556闋�绗�557闋�绗�558闋�绗�559闋�绗�560闋�绗�561闋�绗�562闋�绗�563闋�绗�564闋�绗�565闋�绗�566闋�绗�567闋�绗�568闋�绗�569闋�绗�570闋�绗�571闋�绗�572闋�绗�573闋�绗�574闋�绗�575闋�绗�576闋�绗�577闋�绗�578闋�绗�579闋�绗�580闋�绗�581闋�绗�582闋�绗�583闋�绗�584闋�绗�585闋�绗�586闋�绗�587闋�绗�588闋�绗�589闋�绗�590闋�绗�591闋�绗�592闋�绗�593闋�绗�594闋�绗�595闋�绗�596闋�绗�597闋�绗�598闋�绗�599闋�绗�600闋�绗�601闋�绗�602闋�绗�603闋�绗�604闋�绗�605闋�绗�606闋�绗�607闋�绗�608闋�绗�609闋�绗�610闋�绗�611闋�绗�612闋�绗�613闋�绗�614闋�绗�615闋�绗�616闋�绗�617闋�绗�618闋�绗�619闋�绗�620闋�绗�621闋�绗�622闋�绗�623闋�绗�624闋�绗�625闋�绗�626闋�绗�627闋�绗�628闋�绗�629闋�绗�630闋�绗�631闋�绗�632闋�绗�633闋�绗�634闋�绗�635闋�绗�636闋�绗�637闋�绗�638闋�绗�639闋�绗�640闋�绗�641闋�绗�642闋�绗�643闋�绗�644闋�绗�645闋�绗�646闋�绗�647闋�绗�648闋�绗�649闋�绗�650闋�绗�651闋�绗�652闋�绗�653闋�绗�654闋�绗�655闋�绗�656闋�绗�657闋�绗�658闋�绗�659闋�绗�660闋�绗�661闋�绗�662闋�绗�663闋�绗�664闋�绗�665闋�绗�666闋�绗�667闋�绗�668闋�绗�669闋�绗�670闋�绗�671闋�绗�672闋�绗�673闋�绗�674闋�绗�675闋�绗�676闋�绗�677闋�绗�678闋�绗�679闋�绗�680闋�绗�681闋�绗�682闋�绗�683闋�绗�684闋�绗�685闋�绗�686闋�绗�687闋�绗�688闋�绗�689闋�绗�690闋�绗�691闋�绗�692闋�绗�693闋�绗�694闋�绗�695闋�绗�696闋�绗�697闋�绗�698闋�绗�699闋�绗�700闋�绗�701闋�绗�702闋�绗�703闋�绗�704闋�绗�705闋�绗�706闋�绗�707闋�绗�708闋�绗�709闋�绗�710闋�绗�711闋�绗�712闋�绗�713闋�绗�714闋�绗�715闋�绗�716闋�绗�717闋�绗�718闋�绗�719闋�绗�720闋�绗�721闋�绗�722闋�绗�723闋�绗�724闋�绗�725闋�绗�726闋�绗�727闋�绗�728闋�绗�729闋�绗�730闋�绗�731闋�绗�732闋�绗�733闋�绗�734闋�绗�735闋�绗�736闋�绗�737闋�绗�738闋�绗�739闋�绗�740闋�绗�741闋�绗�742闋�绗�743闋�绗�744闋�绗�745闋�绗�746闋�绗�747闋�绗�748闋�绗�749闋�绗�750闋�绗�751闋�绗�752闋�绗�753闋�绗�754闋�绗�755闋�绗�756闋�绗�757闋�绗�758闋�绗�759闋�绗�760闋�绗�761闋�绗�762闋�绗�763闋�绗�764闋�绗�765闋�绗�766闋�绗�767闋�绗�768闋�

3鈥�8

Altera Corporation

Stratix II Device Handbook, Volume 1

May 2007

Configuration

f

See the Configuring Stratix II & Stratix II GX Devices chapter in volume 2

of the Stratix II Device Handbook or the Stratix II GX Device Handbook for

more information about configuration schemes in Stratix II and

Stratix II GX devices.

Device Security Using Configuration Bitstream Encryption

Stratix II FPGAs are the industry鈥檚 first FPGAs with the ability to decrypt

a configuration bitstream using the Advanced Encryption Standard

(AES) algorithm. When using the design security feature, a 128-bit

security key is stored in the Stratix II FPGA. To successfully configure a

Stratix II FPGA that has the design security feature enabled, it must be

configured with a configuration file that was encrypted using the same

128-bit security key. The security key can be stored in non-volatile

memory inside the Stratix II device. This non-volatile memory does not

require any external devices, such as a battery back-up, for storage.

PPA

MAX II device or microprocessor and

flash device

v

JTAG

Download cable (4)

MAX II device or microprocessor and

flash device

Notes for Table 3鈥�5:

(1)

In these modes, the host system must send a DCLK that is 4脳 the data rate.

(2)

The enhanced configuration device decompression feature is available, while the Stratix II decompression feature

is not available.

(3)

Only remote update mode is supported when using the AS configuration scheme. Local update mode is not

supported.

(4)

The supported download cables include the Altera USB Blaster universal serial bus (USB) port download cable,

MasterBlaster serial/USB communications cable, ByteBlaster II parallel port download cable, and the

ByteBlasterMV parallel port download cable.

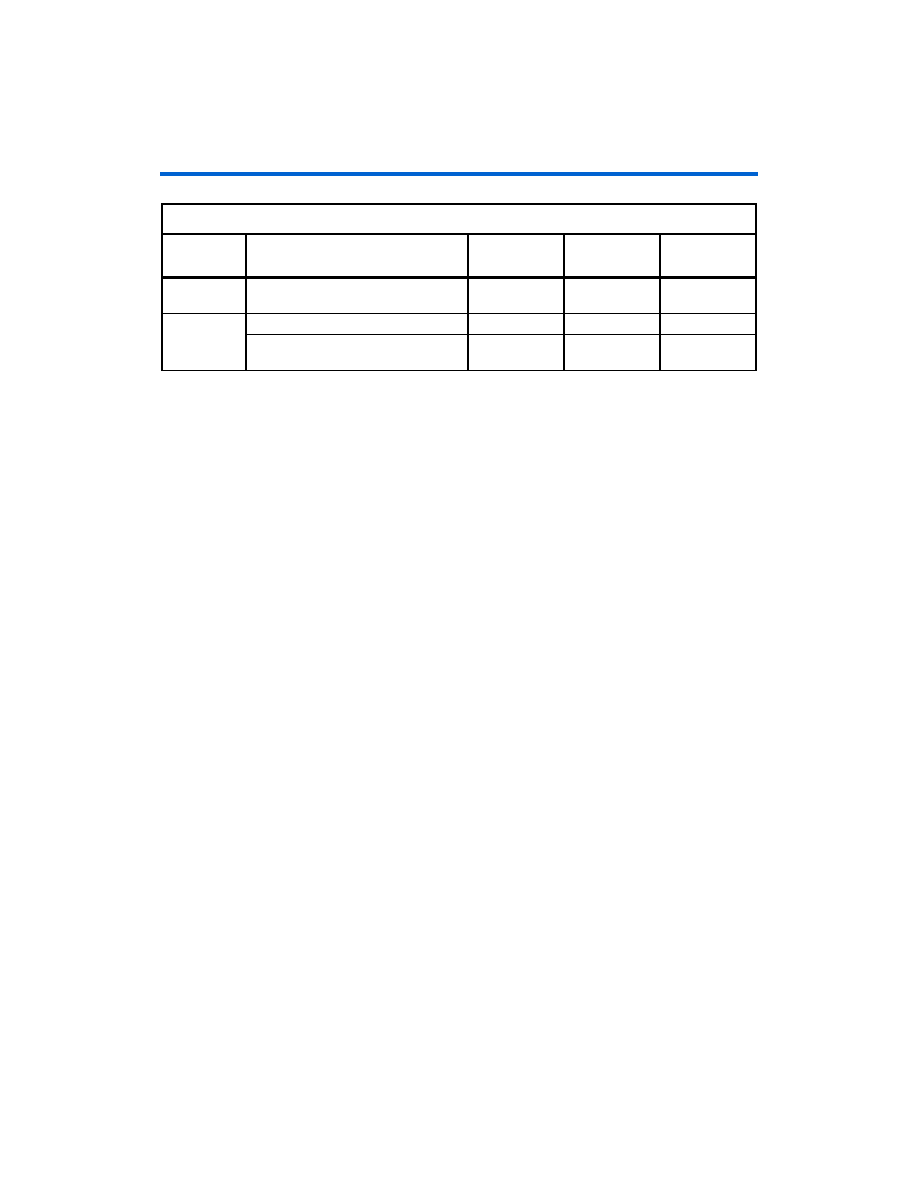

Table 3鈥�5. Stratix II Configuration Features (Part 2 of 2)

Configuration

Scheme

Configuration Method

Design Security Decompression

Remote System

Upgrade

鐩搁棞PDF璩囨枡 |

PDF鎻忚堪 |

|---|---|

| EP2AGX95DF25C5N | IC ARRIA II GX FPGA 95K 572FBGA |

| EP1S20F484C5 | IC STRATIX FPGA 20K LE 484-FBGA |

| 445705-4 | CONN D-SUB RCPT HSING 3C3 MIX |

| ACC50DRXS-S734 | CONN EDGECARD 100PS DIP .100 SLD |

| 204501-5 | CONN D-SUB PLUG HD 15P SER 90 |

鐩搁棞浠g悊鍟�/鎶€琛撳弮鏁� |

鍙冩暩鎻忚堪 |

|---|---|

| EP2S30F672C3N | 鍔熻兘鎻忚堪:FPGA - 鐝惧牬鍙法绋嬮杸闄e垪 FPGA - Stratix II 1694 LABs 500 IOs RoHS:鍚� 鍒堕€犲晢:Altera Corporation 绯诲垪:Cyclone V E 鏌垫サ鏁搁噺: 閭忚集濉婃暩閲�:943 鍏у祵寮忓RAM - EBR:1956 kbit 杓稿叆/杓稿嚭绔暩閲�:128 鏈€澶у伐浣滈牷鐜�:800 MHz 宸ヤ綔闆绘簮闆诲:1.1 V 鏈€澶у伐浣滄韩搴�:+ 70 C 瀹夎棰ㄦ牸:SMD/SMT 灏佽 / 绠遍珨:FBGA-256 |

| EP2S30F672C4 | 鍔熻兘鎻忚堪:FPGA - 鐝惧牬鍙法绋嬮杸闄e垪 FPGA - Stratix II 1694 LABs 500 IOs RoHS:鍚� 鍒堕€犲晢:Altera Corporation 绯诲垪:Cyclone V E 鏌垫サ鏁搁噺: 閭忚集濉婃暩閲�:943 鍏у祵寮忓RAM - EBR:1956 kbit 杓稿叆/杓稿嚭绔暩閲�:128 鏈€澶у伐浣滈牷鐜�:800 MHz 宸ヤ綔闆绘簮闆诲:1.1 V 鏈€澶у伐浣滄韩搴�:+ 70 C 瀹夎棰ㄦ牸:SMD/SMT 灏佽 / 绠遍珨:FBGA-256 |

| EP2S30F672C4N | 鍔熻兘鎻忚堪:FPGA - 鐝惧牬鍙法绋嬮杸闄e垪 FPGA - Stratix II 1694 LABs 500 IOs RoHS:鍚� 鍒堕€犲晢:Altera Corporation 绯诲垪:Cyclone V E 鏌垫サ鏁搁噺: 閭忚集濉婃暩閲�:943 鍏у祵寮忓RAM - EBR:1956 kbit 杓稿叆/杓稿嚭绔暩閲�:128 鏈€澶у伐浣滈牷鐜�:800 MHz 宸ヤ綔闆绘簮闆诲:1.1 V 鏈€澶у伐浣滄韩搴�:+ 70 C 瀹夎棰ㄦ牸:SMD/SMT 灏佽 / 绠遍珨:FBGA-256 |

| EP2S30F672C5 | 鍔熻兘鎻忚堪:FPGA - 鐝惧牬鍙法绋嬮杸闄e垪 FPGA - Stratix II 1694 LABs 500 IOs RoHS:鍚� 鍒堕€犲晢:Altera Corporation 绯诲垪:Cyclone V E 鏌垫サ鏁搁噺: 閭忚集濉婃暩閲�:943 鍏у祵寮忓RAM - EBR:1956 kbit 杓稿叆/杓稿嚭绔暩閲�:128 鏈€澶у伐浣滈牷鐜�:800 MHz 宸ヤ綔闆绘簮闆诲:1.1 V 鏈€澶у伐浣滄韩搴�:+ 70 C 瀹夎棰ㄦ牸:SMD/SMT 灏佽 / 绠遍珨:FBGA-256 |

| EP2S30F672C5AA | 鍒堕€犲晢:Altera Corporation 鍔熻兘鎻忚堪:FPGA Stratix |

鐧�(f膩)甯冪穵鎬ラ噰璩�锛�3鍒嗛悩宸﹀彸鎮ㄥ皣寰楀埌鍥炲京銆�