- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄97914 > EP20K1000CF1020I8ES Single Volatile 128-Tap Digitally Controlled Potentiometer (XDCP™); Temperature Range: -40°C to 85°C; Package: 6-SC-70 PDF資料下載

參數(shù)資料

| 型號: | EP20K1000CF1020I8ES |

| 元件分類: | 數(shù)字電位計 |

| 英文描述: | Single Volatile 128-Tap Digitally Controlled Potentiometer (XDCP™); Temperature Range: -40°C to 85°C; Package: 6-SC-70 |

| 中文描述: | 專用集成電路 |

| 文件頁數(shù): | 20/114頁 |

| 文件大?。?/td> | 1623K |

| 代理商: | EP20K1000CF1020I8ES |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁

Altera Corporation

13

APEX 20K Programmable Logic Device Family Data Sheet

Logic Element

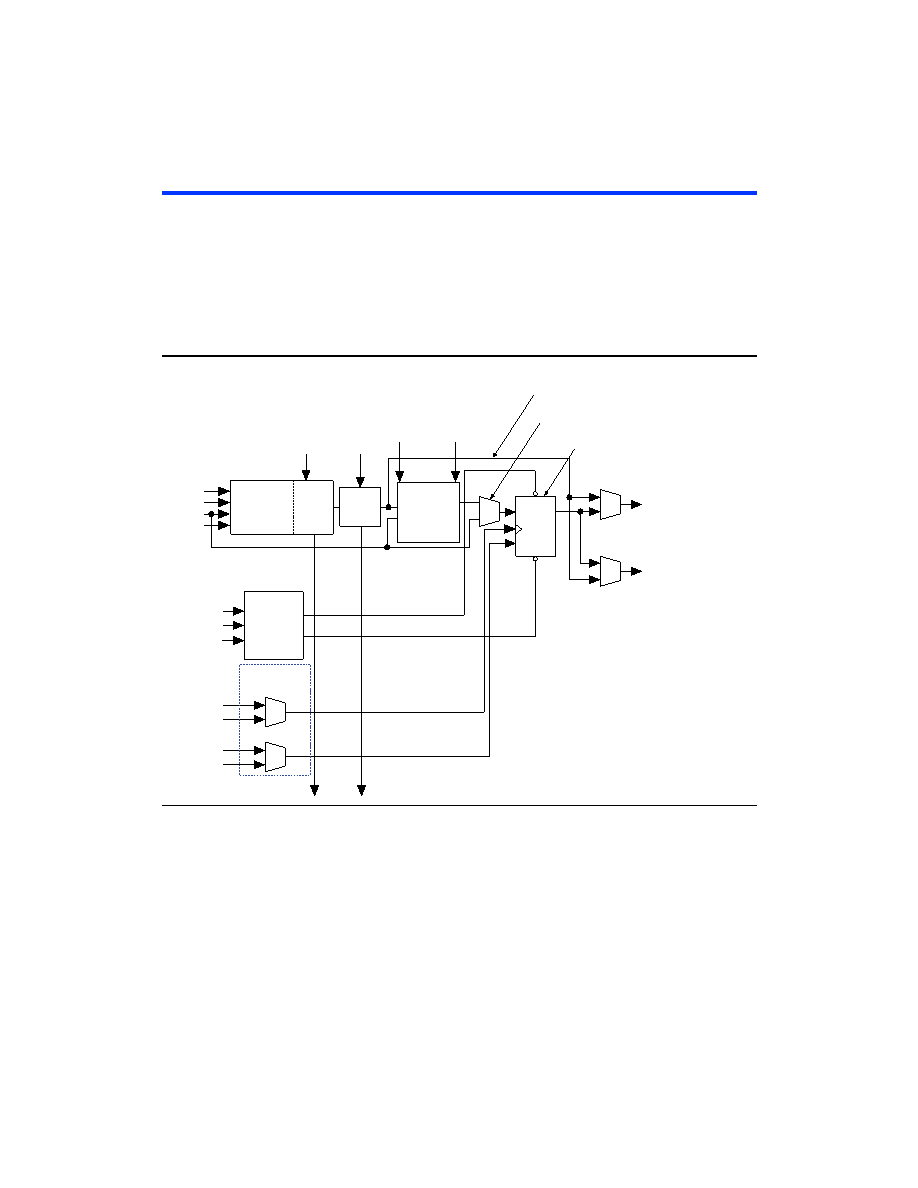

The LE, the smallest unit of logic in the APEX 20K architecture, is compact

and provides efficient logic usage. Each LE contains a four-input LUT,

which is a function generator that can quickly implement any function of

four variables. In addition, each LE contains a programmable register and

carry and cascade chains. Each LE drives the local interconnect, MegaLAB

interconnect, and FastTrack Interconnect routing structures. See Figure 5.

Figure 5. APEX 20K Logic Element

Each LE’s programmable register can be configured for D, T, JK, or SR

operation. The register’s clock and clear control signals can be driven by

global signals, general-purpose I/O pins, or any internal logic. For

combinatorial functions, the register is bypassed and the output of the

LUT drives the outputs of the LE.

labclk1

labclk2

labclr1

labclr2

Carry-In

Clock &

Clock Enable

Select

Carry-Out

Look-Up

Table

(LUT)

Carry

Chain

Cascade

Chain

Cascade-In

Cascade-Out

To FastTrack Interconnect,

MegaLAB Interconnect,

or Local Interconnect

To FastTrack Interconnect,

MegaLAB Interconnect,

or Local Interconnect

Programmable

Register

PRN

CLRN

DQ

ENA

Register Bypass

Packed

Register Select

Chip-Wide

Reset

labclkena1

labclkena2

Synchronous

Load & Clear

Logic

LAB-wide

Synchronous

Load

LAB-wide

Synchronous

Clear

Asynchronous

Clear/Preset/

Load Logic

data1

data2

data3

data4

相關PDF資料 |

PDF描述 |

|---|---|

| EP20K1000CF1020I9ES | ASIC |

| EP20K1000CF33C7 | FPGA |

| EP20K1000CF33C8 | FPGA |

| EP20K1000CF33C9 | FPGA |

| EP20K1000CF33I8 | Single Digitally Controlled Potentiometer (XDCP™), Low Noise/Low Power/I2C Bus/256 Taps; Temperature Range: -25°C to 85°C; Package: 8-MSOP |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| EP20K1000CF1020I9ES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| EP20K1000CF33C7 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 CPLD - APEX 20K 2560 Macros 1.8 V RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP20K1000CF33C7NJ | 制造商:Altera Corporation 功能描述:FPGA APEX 20KC Family 1M Gates 38400 Cells 375.94MHz 0.15um (CMOS) Technology 1.8V 1020-Pin FC-FBGA |

| EP20K1000CF33C8 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 CPLD - APEX 20K 2560 Macros 1.8 V RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP20K1000CF33C9 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 CPLD - APEX 20K 2560 Macro 1.8 V RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復。