- 鎮ㄧ従(xi脿n)鍦ㄧ殑浣嶇疆锛�璨疯常IC缍�(w菐ng) > PDF鐩寗4494 > EP1K50QI208-2N (Altera)IC ACEX 1K FPGA 50K 208-PQFP PDF璩囨枡涓嬭級

鍙冩暩(sh霉)璩囨枡

| 鍨嬭櫉(h脿o)锛� | EP1K50QI208-2N |

| 寤犲晢锛� | Altera |

| 鏂囦欢闋�(y猫)鏁�(sh霉)锛� | 62/86闋�(y猫) |

| 鏂囦欢澶у皬锛� | 0K |

| 鎻忚堪锛� | IC ACEX 1K FPGA 50K 208-PQFP |

| 鐢�(ch菐n)鍝佸煿瑷�(x霉n)妯″锛� | Three Reasons to Use FPGA's in Industrial Designs |

| 妯�(bi膩o)婧�(zh菙n)鍖呰锛� | 144 |

| 绯诲垪锛� | ACEX-1K® |

| LAB/CLB鏁�(sh霉)锛� | 360 |

| 閭忚集鍏冧欢/鍠厓鏁�(sh霉)锛� | 2880 |

| RAM 浣嶇附瑷�(j矛)锛� | 40960 |

| 杓稿叆/杓稿嚭鏁�(sh霉)锛� | 147 |

| 闁€鏁�(sh霉)锛� | 199000 |

| 闆绘簮闆诲锛� | 2.375 V ~ 2.625 V |

| 瀹夎椤炲瀷锛� | 琛ㄩ潰璨艰 |

| 宸ヤ綔婧害锛� | -40°C ~ 100°C |

| 灏佽/澶栨锛� | 208-BFQFP |

| 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁濓細 | 208-PQFP锛�28x28锛� |

| 鍏跺畠鍚嶇ū锛� | 544-1846 EP1K50QI208-2N-ND |

绗�1闋�(y猫)绗�2闋�(y猫)绗�3闋�(y猫)绗�4闋�(y猫)绗�5闋�(y猫)绗�6闋�(y猫)绗�7闋�(y猫)绗�8闋�(y猫)绗�9闋�(y猫)绗�10闋�(y猫)绗�11闋�(y猫)绗�12闋�(y猫)绗�13闋�(y猫)绗�14闋�(y猫)绗�15闋�(y猫)绗�16闋�(y猫)绗�17闋�(y猫)绗�18闋�(y猫)绗�19闋�(y猫)绗�20闋�(y猫)绗�21闋�(y猫)绗�22闋�(y猫)绗�23闋�(y猫)绗�24闋�(y猫)绗�25闋�(y猫)绗�26闋�(y猫)绗�27闋�(y猫)绗�28闋�(y猫)绗�29闋�(y猫)绗�30闋�(y猫)绗�31闋�(y猫)绗�32闋�(y猫)绗�33闋�(y猫)绗�34闋�(y猫)绗�35闋�(y猫)绗�36闋�(y猫)绗�37闋�(y猫)绗�38闋�(y猫)绗�39闋�(y猫)绗�40闋�(y猫)绗�41闋�(y猫)绗�42闋�(y猫)绗�43闋�(y猫)绗�44闋�(y猫)绗�45闋�(y猫)绗�46闋�(y猫)绗�47闋�(y猫)绗�48闋�(y猫)绗�49闋�(y猫)绗�50闋�(y猫)绗�51闋�(y猫)绗�52闋�(y猫)绗�53闋�(y猫)绗�54闋�(y猫)绗�55闋�(y猫)绗�56闋�(y猫)绗�57闋�(y猫)绗�58闋�(y猫)绗�59闋�(y猫)绗�60闋�(y猫)绗�61闋�(y猫)鐣�(d膩ng)鍓嶇62闋�(y猫)绗�63闋�(y猫)绗�64闋�(y猫)绗�65闋�(y猫)绗�66闋�(y猫)绗�67闋�(y猫)绗�68闋�(y猫)绗�69闋�(y猫)绗�70闋�(y猫)绗�71闋�(y猫)绗�72闋�(y猫)绗�73闋�(y猫)绗�74闋�(y猫)绗�75闋�(y猫)绗�76闋�(y猫)绗�77闋�(y猫)绗�78闋�(y猫)绗�79闋�(y猫)绗�80闋�(y猫)绗�81闋�(y猫)绗�82闋�(y猫)绗�83闋�(y猫)绗�84闋�(y猫)绗�85闋�(y猫)绗�86闋�(y猫)

Altera Corporation

65

ACEX 1K Programmable Logic Device Family Data Sheet

D

e

ve

lo

pm

e

n

t

13

To

o

ls

Notes to tables:

(1)

(2)

This parameter is measured without the use of the ClockLock or ClockBoost circuits.

(3)

These parameters are specified by characterization.

(4)

This parameter is measured with the use of the ClockLock or ClockBoost circuits.

parameters.

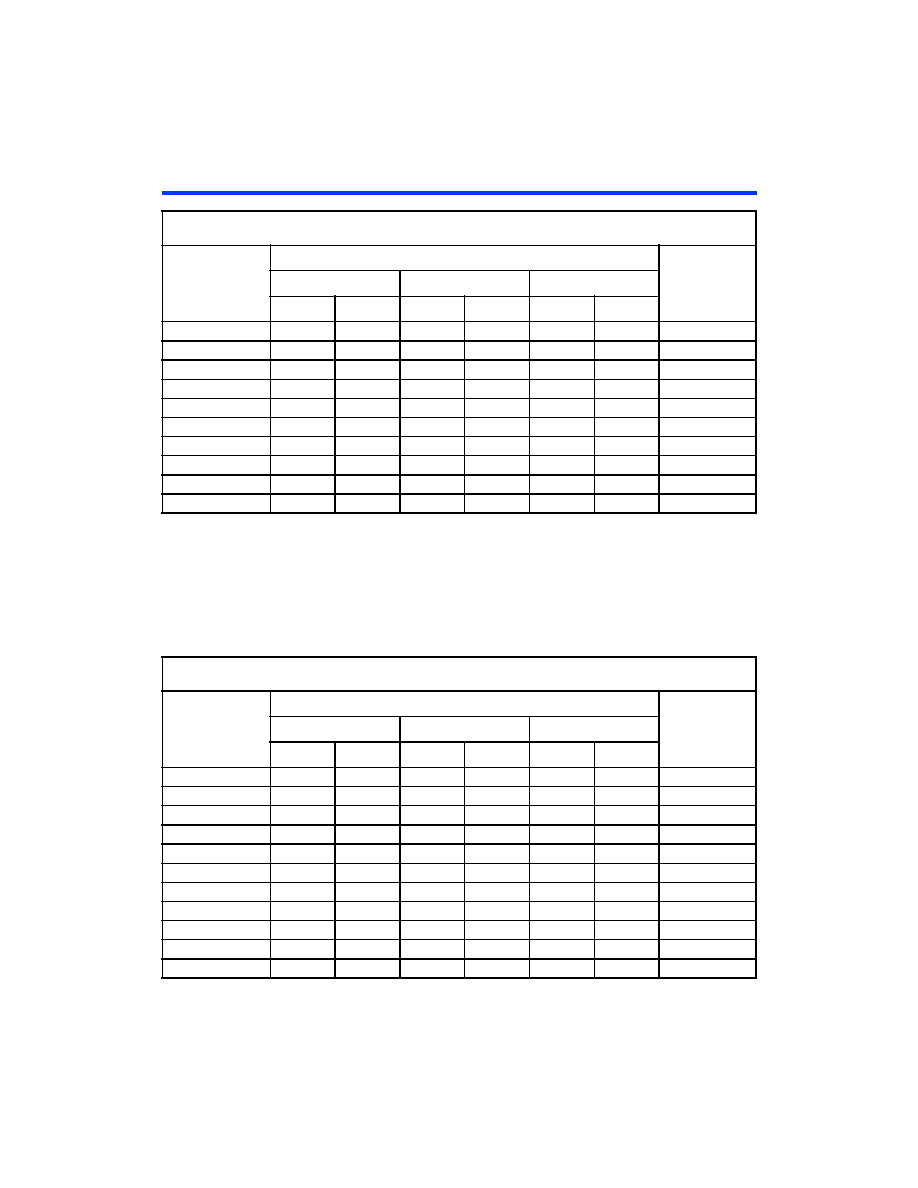

Table 36. EP1K10 External Bidirectional Timing Parameters

Symbol

Speed Grade

Unit

-1

-2

-3

Min

Max

Min

Max

Min

Max

2.2

2.3

3.2

ns

0.0

ns

2.0

6.6

2.0

7.8

2.0

9.6

ns

8.8

11.2

14.0

ns

8.8

11.2

14.0

ns

3.1

3.3

鈥�

0.0

鈥�

0.5

5.1

0.5

6.4

鈥�

ns

7.3

9.2

鈥�

ns

7.3

9.2

鈥�

ns

Table 37. EP1K30 Device LE Timing Microparameters (Part 1 of 2)

Symbol

Speed Grade

Unit

-1

-2

-3

Min

Max

Min

Max

Min

Max

tLUT

0.7

0.8

1.1

ns

tCLUT

0.5

0.6

0.8

ns

tRLUT

0.6

0.7

1.0

ns

tPACKED

0.3

0.4

0.5

ns

tEN

0.6

0.8

1.0

ns

tCICO

0.1

0.2

ns

tCGEN

0.4

0.5

0.7

ns

tCGENR

0.1

0.2

ns

tCASC

0.6

0.8

1.0

ns

tC

0.0

ns

tCO

0.3

0.4

0.5

ns

鐩搁棞(gu膩n)PDF璩囨枡 |

PDF鎻忚堪 |

|---|---|

| EP1K50QI208-2 | IC ACEX 1K FPGA 50K 208-PQFP |

| A3P250L-1FGG144I | IC FPGA 1KB FLASH 250K 144-FBGA |

| ASM31DTMD-S189 | CONN EDGECARD 62POS R/A .156 SLD |

| AGM31DTMD-S189 | CONN EDGECARD 62POS R/A .156 SLD |

| AYM31DTBN-S189 | CONN EDGECARD 62POS R/A .156 SLD |

鐩搁棞(gu膩n)浠g悊鍟�/鎶€琛�(sh霉)鍙冩暩(sh霉) |

鍙冩暩(sh霉)鎻忚堪 |

|---|---|

| EP1K50QI208-2P | 鍒堕€犲晢:鏈煡寤犲 鍒堕€犲晢鍏ㄧū:鏈煡寤犲 鍔熻兘鎻忚堪:Field Programmable Gate Array (FPGA) |

| EP1K50QI208-2X | 鍒堕€犲晢:鏈煡寤犲 鍒堕€犲晢鍏ㄧū:鏈煡寤犲 鍔熻兘鎻忚堪:Field Programmable Gate Array (FPGA) |

| EP1K50QI208-3F | 鍒堕€犲晢:鏈煡寤犲 鍒堕€犲晢鍏ㄧū:鏈煡寤犲 鍔熻兘鎻忚堪:Field Programmable Gate Array (FPGA) |

| EP1K50TC144-1 | 鍔熻兘鎻忚堪:FPGA - 鐝�(xi脿n)鍫�(ch菐ng)鍙法绋嬮杸闄e垪 FPGA - ACEX 1K 360 LABs 102 IOs RoHS:鍚� 鍒堕€犲晢:Altera Corporation 绯诲垪:Cyclone V E 鏌垫サ鏁�(sh霉)閲�: 閭忚集濉婃暩(sh霉)閲�:943 鍏�(n猫i)宓屽紡濉奟AM - EBR:1956 kbit 杓稿叆/杓稿嚭绔暩(sh霉)閲�:128 鏈€澶у伐浣滈牷鐜�:800 MHz 宸ヤ綔闆绘簮闆诲:1.1 V 鏈€澶у伐浣滄韩搴�:+ 70 C 瀹夎棰�(f膿ng)鏍�:SMD/SMT 灏佽 / 绠遍珨:FBGA-256 |

| EP1K50TC144-1DX | 鍒堕€犲晢:鏈煡寤犲 鍒堕€犲晢鍏ㄧū:鏈煡寤犲 鍔熻兘鎻忚堪:Field Programmable Gate Array (FPGA) |

鐧�(f膩)甯冪穵鎬ラ噰璩�(g貌u)锛�3鍒嗛悩宸﹀彸鎮ㄥ皣寰楀埌鍥炲京(f霉)銆�