- 您現(xiàn)在的位置:買賣IC網 > PDF目錄384280 > EDE5104AGSE-6C-E (ELPIDA MEMORY INC) LJT 6C 6#20 SKT RECP PDF資料下載

參數(shù)資料

| 型號: | EDE5104AGSE-6C-E |

| 廠商: | ELPIDA MEMORY INC |

| 元件分類: | DRAM |

| 英文描述: | LJT 6C 6#20 SKT RECP |

| 中文描述: | 128M X 4 DDR DRAM, 0.45 ns, PBGA60 |

| 封裝: | ROHS COMPLIANT, FBGA-60 |

| 文件頁數(shù): | 37/66頁 |

| 文件大小: | 697K |

| 代理商: | EDE5104AGSE-6C-E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁

EDE5104ABSE, EDE5108ABSE, EDE5116ABSE

Data Sheet E0323E90 (Ver. 9.0)

37

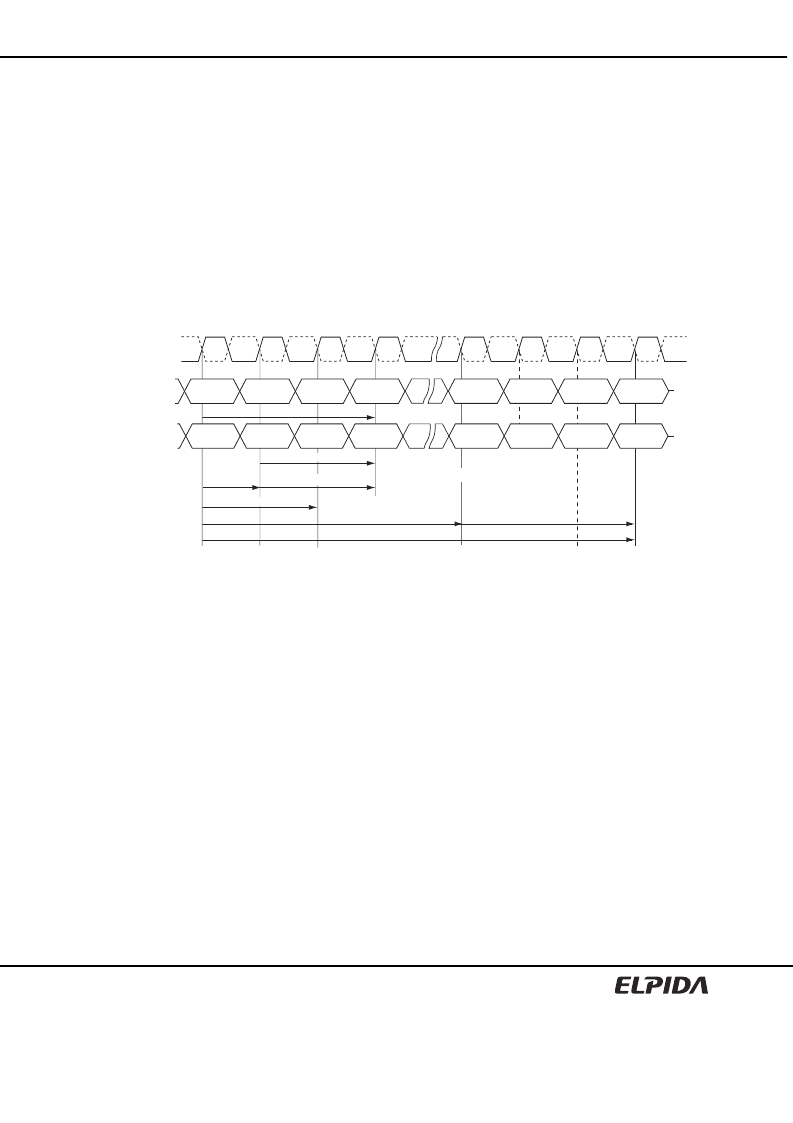

Bank Activate Command [ACT]

The bank activate command is issued by holding /CAS and /WE high with /CS and /RAS low at the rising edge of the

clock. The bank addresses BA0 and BA1, are used to select the desired bank. The row address A0 through A13 is

used to determine which row to activate in the selected bank. The Bank activate command must be applied before

any read or write operation can be executed. Immediately after the bank active command, the DDR2 SDRAM can

accept a read or write command on the following clock cycle. If a R/W command is issued to a bank that has not

satisfied the tRCD (min.) specification, then additive latency must be programmed into the device to delay when the

R/W command is internally issued to the device. The additive latency value must be chosen to assure tRCD (min.)

is satisfied. Additive latencies of 0, 1, 2, 3 and 4 are supported. Once a bank has been activated it must be

precharged before another bank activate command can be applied to the same bank. The bank active and

precharge times are defined as tRAS and tRP, respectively. The minimum time interval between successive bank

activate commands to the same bank is determined by the /RAS cycle time of the device (tRC), which is equal to

tRAS + tRP. The minimum time interval between successive bank activate commands to the different bank is

determined by (tRRD).

/CK

CK

Address

Command

T0

T1

T2

T3

Tn

Tn+1

Tn+2

Tn+3

tRCD(min.)

tRAS

tRP

tRC

ROW: 0

ACT

Bank0

Active

Bank Activate Command Cycle (tRCD = 3, AL = 2, tRP = 3, tRRD = 2, tCCD = 2)

Bank1

Active

Bank0

Active

Bank0

Precharge

Bank1

Precharge

Posted

READ

Posted

READ

ACT

PRE

PRE

ACT

COL: 0

ROW: 0

ROW: 1

COL: 1

tRCD =1

tCCD

Additive latency (AL)

tRRD

Bank0 Read begins

相關PDF資料 |

PDF描述 |

|---|---|

| EDE5108AGSE-6C-E | LJT 13C 13#22M PIN RECP |

| EDE5104AGSE-6E-E | Circular Connector; No. of Contacts:13; Series:MS27468; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:11; Circular Contact Gender:Socket; Circular Shell Style:Jam Nut Receptacle; Insert Arrangement:11-13 RoHS Compliant: No |

| EDE5108AGSE-6E-E | Circular Connector; No. of Contacts:2; Series:MS27468; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:11; Circular Contact Gender:Socket; Circular Shell Style:Jam Nut Receptacle; Insert Arrangement:11-2 RoHS Compliant: No |

| EDE5104ABSE-4A-E | 512M bits DDR2 SDRAM |

| EDE5108ABSE-4A-E | 512M bits DDR2 SDRAM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| EDE5104AGSE-6E-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:512M bits DDR2 SDRAM |

| EDE5104AHSE | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:512M bits DDR2 SDRAM |

| EDE5104AHSE-6E-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:512M bits DDR2 SDRAM |

| EDE5104AJBG | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:512M bits DDR2 SDRAM |

| EDE5104AJBG-6E-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:512M bits DDR2 SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。