- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄2068 > DS3510T+ (Maxim Integrated Products)IC I2C GAMMA/VCOM BUFF 48-TQFN PDF資料下載

參數(shù)資料

| 型號: | DS3510T+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 2/17頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC I2C GAMMA/VCOM BUFF 48-TQFN |

| 產(chǎn)品培訓模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標準包裝: | 209 |

| 應用: | TFT-LCD 面板:伽瑪緩沖器,VCOM 驅(qū)動器 |

| 輸出類型: | 滿擺幅 |

| 電路數(shù): | 10 |

| 電流 - 電源: | 6.7mA |

| 電流 - 輸出 / 通道: | 4mA |

| 電壓 - 電源,單路/雙路(±): | 9 V ~ 15 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 48-WFQFN 裸露焊盤 |

| 供應商設備封裝: | 48-TQFN-EP(7x7) |

| 包裝: | 管件 |

DS3510

I2C Gamma and VCOM Buffer with EEPROM

10

______________________________________________________________________________________

Detailed Description

The DS3510 operates in one of three modes which

determine how the VCOM and gamma DACs are con-

trolled/updated. The first two modes allow “banked”

control of the 10 gamma channels and 1 VCOM chan-

nel. Depending on the mode, one of four banks (in

EEPROM) can be selected using either the S0/S1 pins

or using the SOFT S0/S1 bits in the Soft S0/S1 register.

Once a bank is selected, the LD pin can then be used

to simultaneously update each channel’s DAC output.

The third and final mode is not banked. It allows I2C

control of each channel’s Latch A register which is

SRAM (volatile), allowing quick and unlimited updates.

In this mode, the LD pin can also be used to simultane-

ously update each channel’s DAC output. A detailed

description of the three modes as well as additional

features of the DS3510 follows.

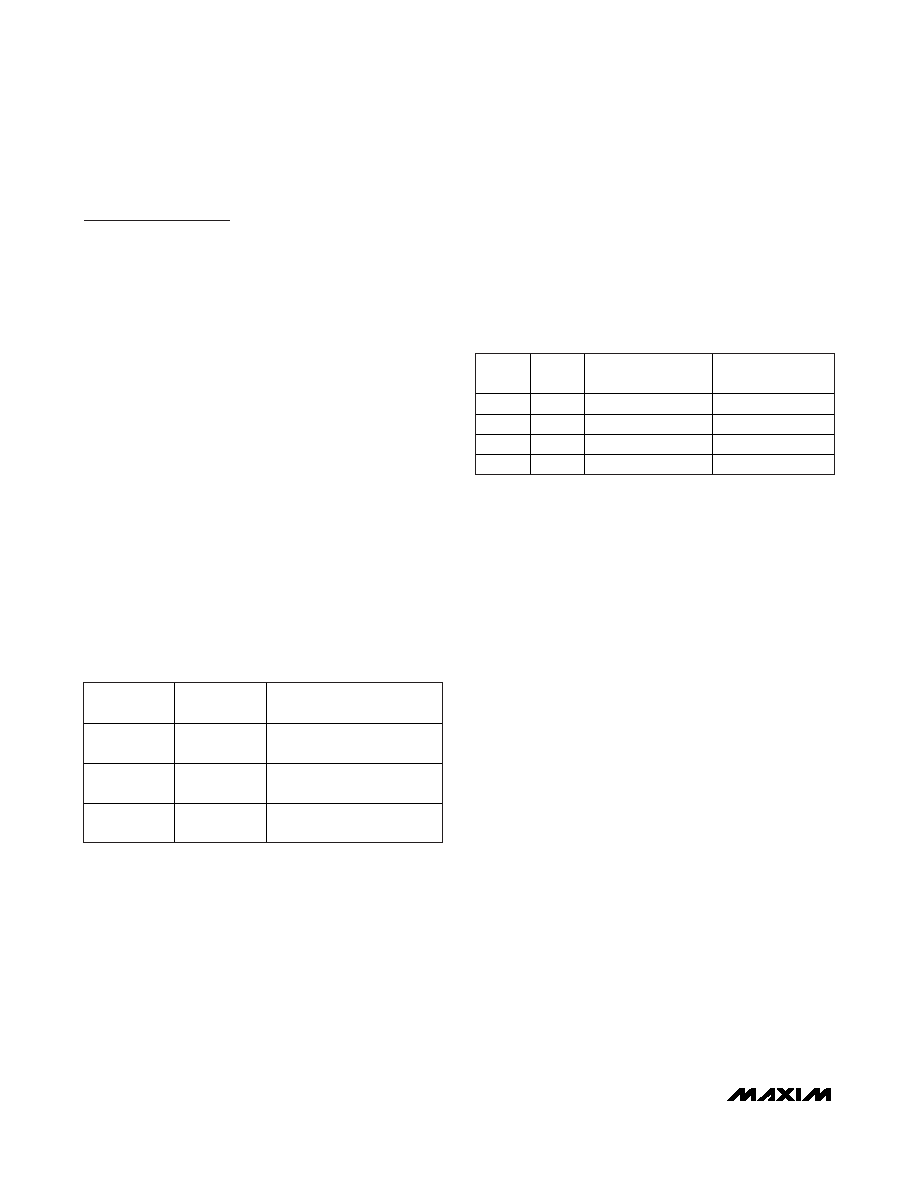

Mode Selection

The DS3510 mode of operation is determined by 2 bits

located in the Control register (60h), which is non-

volatile (NV) (EEPROM). In particular, the mode is

determined by the MODE0 bit (CR.0) and the MODE1

bit (CR.1). Table 1 illustrates how the 2 control bits are

used to select the operating mode. When shipped from

the factory, the DS3510 is programmed with both

MODE bits set to zero.

S0/S1 Pin-Controlled Bank Updating Mode

As shown in the block diagram, each channel contains

4 bytes of EEPROM, which are used to implement the

“banking” functionality. Each “bank” contains unique

DAC settings for each channel. When the DS3510 is

configured in this operating mode, the desired bank is

selected using the S0 and S1 pins as shown in Table 2

where 0 is ground and 1 is VCC. For example, if S0 and

S1 are both connected to ground, then the first bank

(Bank A) is selected. Once a bank is selected, the tim-

ing of the DAC update depends on the state of LD pin.

When LD is high, Latch B functions as a flow-through

latch, so the amplifier will respond asynchronously to

changes in the state of S0/S1 to meet the tSEL specifi-

cation. Conversely, when LD is low, Latch B functions

as a latch, holding its previous data. A low-to-high tran-

sition on LD allows the Latch B input data to flow

through and update the DACs with the EEPROM bank

selected by S0/S1. A high-to-low transition on LD latch-

es the selected DAC data into Latch B.

SOFT S0/S1 (Bit) Controlled Bank

Updating Mode

This mode also features “banked” operation with the

only difference being how the desired bank is selected.

In particular, the bank is selected using the SOFT S0

(bit 0) and SOFT S1 (bit 1) bits contained in the Soft

S0/S1 register (50h). The S0 and S1 pins are ignored in

this mode. Table 2 illustrates the relationship between

the bit settings and the selected bank. For example, if

both bits, S0 and S1, are written to zero, then the first

bank (Bank A) is selected. Once a bank is selected, the

timing of the DAC update depends on the state of the

LD pin. When LD is high, Latch B functions as a flow-

through latch, so the amplifier will respond asynchro-

nously to changes in the state of the S0/S1 bits. These

are changed by an I2C write. Conversely, when LD is

low, Latch B functions as a latch, holding its previous

data. A low-to-high transition on LD allows the Latch B

input data to flow through and update the DACs with

the EEPROM bank selected by the S0/S1 bits. A high-

to-low transition on LD latches the selected DAC data

into Latch B.

Since the Soft S0/S1 register is SRAM, subsequent

power-ups result in the SOFT S0 and SOFT S1 bits

being cleared to 0 and, hence, powering up to Bank A.

I2C Individual Channel Control Mode

In this mode the I2C master writes directly to individual

channel Latch A registers to update a single DAC (i.e.,

not banked). The Latch A registers are SRAM and not

EEPROM. This allows an unlimited number of write

cycles as well as quicker write times since tW only

applies to EEPROM writes. As shown in the

Memory

Map, the Latch A registers for each channel are

accessed through memory addresses 00–0Ah. Then,

MODE1 BIT

(CR.1)

MODE0 BIT

(CR.0)

MODE

0

S0/S1 Pin-Controlled Bank

Updating (Factory Default)

0

1

S0/S1 Bit-Controlled Bank

Updating

1

X

I2C Individual Channel

Control

Table 1. DS3510 Operating Modes

S1

S0

VCOM

CHANNEL

GAMMA

CHANNELS

0

VCOM Bank A

GM1–10 Bank A

0

1

VCOM Bank B

GM1–10 Bank B

1

0

VCOM Bank C

GM1–10 Bank C

1

VCOM Bank D

GM1–10 Bank D

Table 2. DS3510 Bank Selection Table

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS3514T+T&R | IC I2C GAMMA/VCOM BUFF 48-TQFN |

| EL1881CS-T13 | IC VIDEO SYNC SEPARATOR 8-SOIC |

| EL1883IS-T13 | IC VID SYNC SEPARATOR HORZ 8SOIC |

| EL2250CS-T13 | IC OP AMP DUAL 125MHZ 8-SOIC |

| EL4093CSZ-T7 | IC VIDEO AMP 300MHZ 16-SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS3510T+ | 功能描述:LCD Gamma緩沖器 I2C Gamma & VCOM Buffer w/EEPROM RoHS:否 制造商:Maxim Integrated 輸入補償電壓: 轉(zhuǎn)換速度: 電源電壓-最大:20 V 電源電壓-最小:9 V 電源電流: 最大功率耗散: 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:TQFN-38 封裝:Tube |

| DS3510T+T&R | 制造商:Maxim Integrated Products 功能描述: 制造商:Maxim Integrated Products 功能描述:10 CH GAMMA+VCOM 8BIT 48 TQFN T&R L - Tape and Reel 制造商:Maxim Integrated Products 功能描述:IC I2C GAMMA/VCOM BUFF 48-TQFN |

| DS3510T+T&R | 功能描述:LCD Gamma緩沖器 I2C Gamma & VCOM Buffer w/EEPROM RoHS:否 制造商:Maxim Integrated 輸入補償電壓: 轉(zhuǎn)換速度: 電源電壓-最大:20 V 電源電壓-最小:9 V 電源電流: 最大功率耗散: 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:TQFN-38 封裝:Tube |

| DS3510T+TR | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:I2C Gamma and VCOM Buffer with EEPROM |

| DS3511MP000 | 制造商:Thomas & Betts 功能描述:30A,PLG,4P5W,MG,511,220/115V |

發(fā)布緊急采購,3分鐘左右您將得到回復。