- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9753 > DS21448G+ (Maxim Integrated Products)IC LIU E1/T1/J1 QUAD 144-PBGA PDF資料下載

參數(shù)資料

| 型號(hào): | DS21448G+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 14/60頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC LIU E1/T1/J1 QUAD 144-PBGA |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 類型: | 線路接口裝置(LIU) |

| 驅(qū)動(dòng)器/接收器數(shù): | 4/4 |

| 規(guī)程: | T1/E1/J1 |

| 電源電壓: | 3.135 V ~ 3.465 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 144-BGA |

| 供應(yīng)商設(shè)備封裝: | 144-TEPBGA(17x17) |

| 包裝: | 管件 |

| 其它名稱: | 90-21448+G00 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

DS21448 3.3V T1/E1/J1 Quad Line Interface

21 of 60

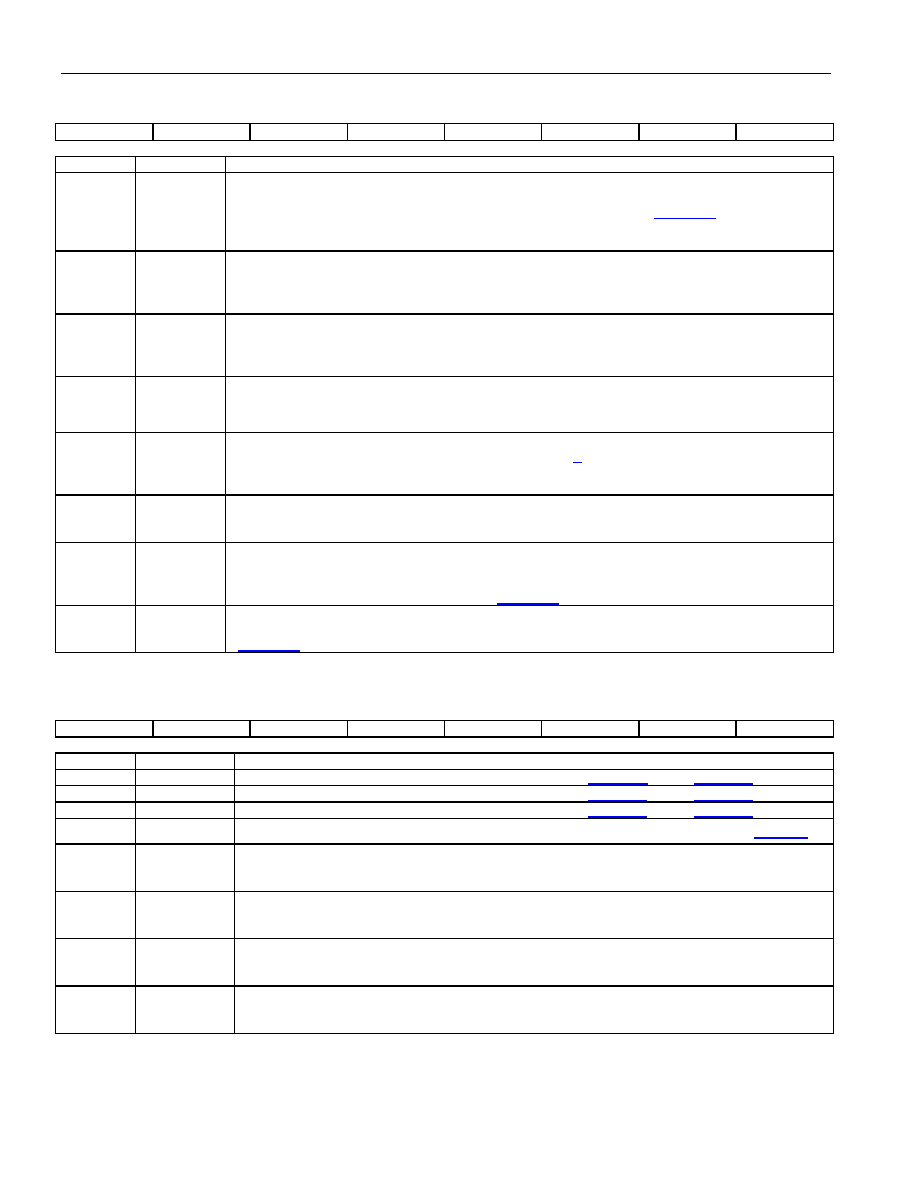

CCR3 (02H): Common Control Register 3

(MSB)

(LSB)

TUA1

ATUA1

TAOZ

TPRBSE

TLCE

LIRST

IBPV

IBE

NAME

POSITION

FUNCTION

TUA1

CCR3.7

Transmit Unframed All Ones. The polarity of this bit is set such that the device transmits an all-

ones pattern on power-up or device reset. This bit must be set to 1 to allow the device to transmit

data. The transmission of this data pattern is always timed off JACLK (Figure 1-1).

0 = transmit all ones at TTIP and TRING

1 = transmit data normally

ATUA1

CCR3.6

Automatic Transmit Unframed All Ones. Automatically transmit an unframed all-ones pattern at

TTIP and TRING during an RCL condition.

0 = disabled

1 = enabled

TAOZ

CCR3.5

Transmit Alternate Ones and Zeros. Transmit a …101010… pattern at TTIP and TRING. The

transmission of this data pattern is always timed off TCLK.

0 = disabled

1 = enabled

TPRBSE

CCR3.4

Transmit PRBS Enable. Transmit a 2

15 - 1 (E1) or a QRSS (T1) PRBS at TTIP and TRING.

0 = disabled

1 = enabled

TLCE

CCR3.3

Transmit Loop-Code Enable. Enables the transmit side to transmit the loop-up code in the transmit

code definition registers (TCD1 and TCD2). See Section 6 for details.

0 = disabled

1 = enabled

LIRST

CCR3.2

Line Interface Reset. Setting this bit from 0 to 1 initiates an internal reset that resets the clock

recovery state machine and recenters the jitter attenuator. Normally this bit is only toggled on

power-up. It must be cleared and set again for a subsequent reset.

IBPV

CCR3.1

Insert Bipolar Violation (BPV). A 0-to-1 transition on this bit causes a single bipolar violation to be

inserted into the transmit data stream. Once this bit has been toggled from 0 to 1, the device waits

for the next occurrence of three consecutive 1s to insert the BPV. This bit must be cleared and set

again for a subsequent error to be inserted (Figure 1-3).

IBE

CCR3.0

Insert Bit Error. A 0-to-1 transition on this bit causes a single logic error to be inserted into the

transmit data stream. This bit must be cleared and set again for a subsequent error to be inserted

CCR4 (03H): Common Control Register 4

(MSB)

(LSB)

L2

L1

L0

EGL

JAS

JABDS

DJA

TPD

NAME

POSITION

FUNCTION

L2

CCR4.7

Line Build-Out Select Bit 2. Sets the transmitter build-out (Table 7-A for E1, Table 7-B for T1).

L1

CCR4.6

Line Build Out Select Bit 1. Sets the transmitter build-out (Table 7-A for E1, Table 7-B for T1).

L0

CCR4.5

Line Build Out Select Bit 0. Sets the transmitter build-out (Table 7-A for E1, Table 7-B for T1).

EGL

CCR4.4

Receive Equalizer Gain Limit. This bit controls the sensitivity of the receive equalizer (Table 4-I).

JAS

CCR4.3

Jitter Attenuator Path Select

0 = place the jitter attenuator on the receive side

1 = place the jitter attenuator on the transmit side

JABDS

CCR4.2

Jitter Attenuator Buffer Depth Select

0 = 128 bits

1 = 32 bits (use for delay-sensitive applications)

DJA

CCR4.1

Disable Jitter Attenuator

0 = jitter attenuator enabled

1 = jitter attenuator disabled

TPD

CCR4.0

Transmit Power-Down

0 = normal transmitter operation

1 = powers down the transmitter and tri-states the TTIP and TRING pins

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC10EP17DTR2G | IC RCVR/DRVR QUAD DIFF 20-TSSOP |

| V375C28M150BF | CONVERTER MOD DC/DC 28V 150W |

| MS3106E20-14S | CONN PLUG 5POS STRAIGHT W/SCKT |

| NB100LVEP17MNR2G | IC DRVR ECL QUAD 2.5V/3.3V 24QFN |

| MX674AKP+ | IC ADC 12BIT W/REF 28-PLCC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS21448G+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 3.3V E1/T1/J1 Quad Interface RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21448GN+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 3.3V E1/T1/J1 Quad Interface RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21448L | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 3.3V E1/T1/J1 Quad Interface RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21448L+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 3.3V E1/T1/J1 Quad Interface RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21448L+W | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 3.3V E1/T1/J1 Quad Interface RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。