- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄97865 > DS1994L-F5 (DALLAS SEMICONDUCTOR) SPECIALTY MEMORY CIRCUIT, MRDB2 PDF資料下載

參數(shù)資料

| 型號(hào): | DS1994L-F5 |

| 廠商: | DALLAS SEMICONDUCTOR |

| 元件分類: | Memory IC:Other |

| 英文描述: | SPECIALTY MEMORY CIRCUIT, MRDB2 |

| 封裝: | MICRO CAN |

| 文件頁(yè)數(shù): | 7/23頁(yè) |

| 文件大小: | 537K |

| 代理商: | DS1994L-F5 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)

DS1992/DS1993/DS1994

15 of 23

102199

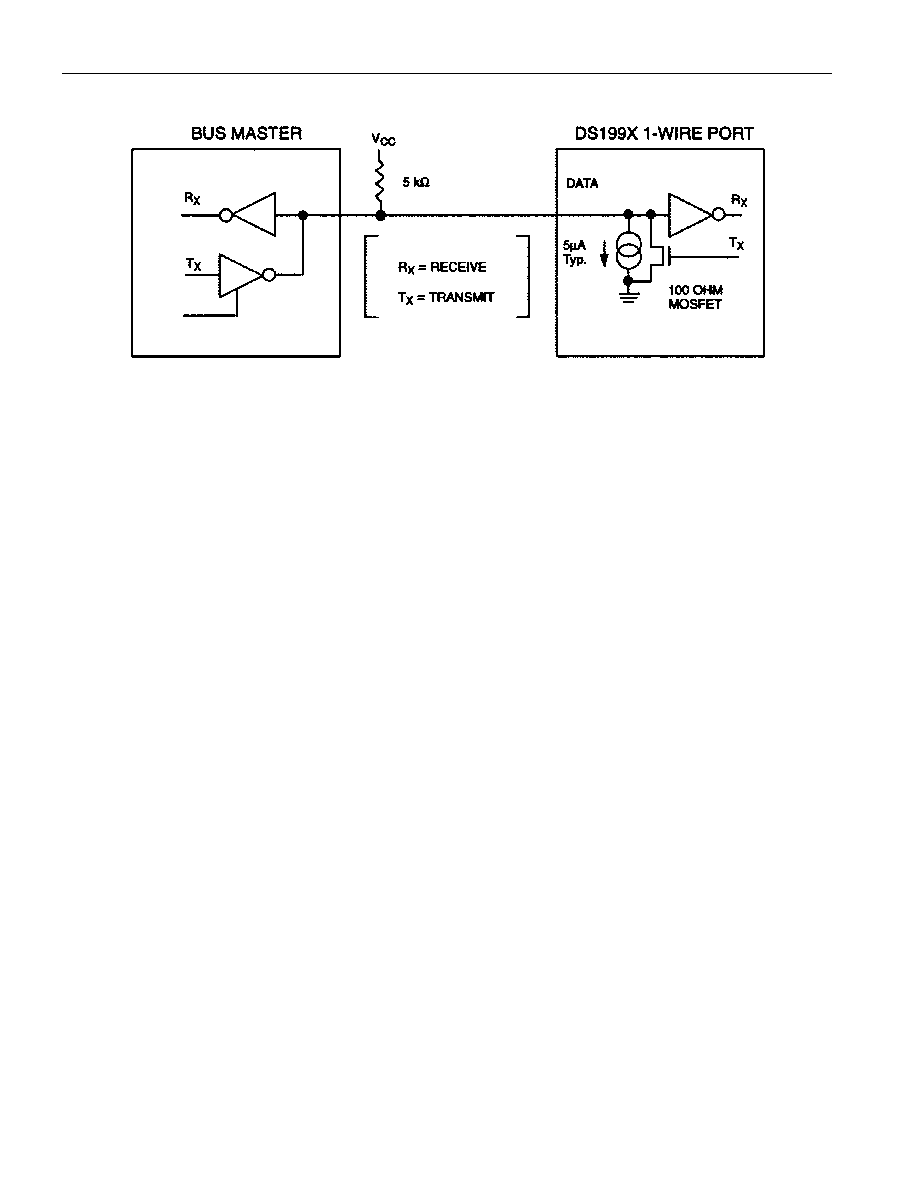

HARDWARE CONFIGURATION Figure 8

TRANSACTION SEQUENCE

The protocol for accessing the DS199X via the 1-wire port is as follows:

§ Initialization

§ ROM Function Command

§ Memory Function Command

§ Transaction/Data

INITIALIZATION

All transactions on the 1-wire bus begin with an initialization sequence. The initialization sequence

consists of a reset pulse transmitted by the bus master followed by presence pulse(s) transmitted by the

slave(s). The presence pulse lets the bus master know that the DS199X is on the bus and is ready to

operate. For more details, see the “1-Wire Signaling” section.

ROM FUNCTION COMMANDS

Once the bus master has detected a presence, it can issue one of the four ROM function commands. All

ROM function commands are eight bits long. A list of these commands follows (refer to flowchart in

Figure 9):

Read ROM [33h]

This command allows the bus master to read the DS199X’s 8-bit family code, unique 48-bit serial num-

ber, and 8-bit CRC. This command can only be used if there is a single DS199X on the bus. If more than

one slave is present on the bus, a data collision will occur when all slaves try to transmit at the same time

(open drain will produce a wired-AND result). The resultant family code and 48–bit serial number will

usually result in a mismatch of the CRC.

Match ROM [55h]

The match ROM command, followed by a 64-bit ROM sequence, allows the bus master to address a

specific DS199X on a multidrop bus. Only the DS199X that exactly matches the 64-bit ROM sequence

will respond to the subsequent memory function command. All slaves that do not match the 64-bit ROM

sequence will wait for a reset pulse. This command can be used with a single or multiple devices on the

bus.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS1993L-F5 | SPECIALTY MEMORY CIRCUIT, MRDB2 |

| DS1992L-F5 | SPECIALTY MEMORY CIRCUIT, MRDB2 |

| DS1996L-F5 | SPECIALTY MEMORY CIRCUIT, MADB2 |

| DS2016 | 2K X 8 STANDARD SRAM, 100 ns, PDIP24 |

| DS2118MB | 9-LINE 110 ohm SCSI BUS TERMINATOR, PDSO36 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS1994L-F5+ | 功能描述:iButton RoHS:否 存儲(chǔ)類型:SRAM 存儲(chǔ)容量:512 B 組織: 工作電源電壓:3 V to 5.25 V 接口類型:1-Wire 最大工作溫度:+ 85 C 尺寸:17.35 mm x 5.89 mm 封裝 / 箱體:F5 MicroCan 制造商:Maxim Integrated |

| DS1994L-F5-W | 功能描述:iButton RoHS:否 存儲(chǔ)類型:SRAM 存儲(chǔ)容量:512 B 組織: 工作電源電壓:3 V to 5.25 V 接口類型:1-Wire 最大工作溫度:+ 85 C 尺寸:17.35 mm x 5.89 mm 封裝 / 箱體:F5 MicroCan 制造商:Maxim Integrated |

| DS1994-LFS | 制造商: 功能描述: 制造商:undefined 功能描述: |

| DS1995 | 制造商:DALLAS 制造商全稱:Dallas Semiconductor 功能描述:16-kbit Memory iButton |

| DS1995L-F5 | 功能描述:iButton RoHS:否 存儲(chǔ)類型:SRAM 存儲(chǔ)容量:512 B 組織: 工作電源電壓:3 V to 5.25 V 接口類型:1-Wire 最大工作溫度:+ 85 C 尺寸:17.35 mm x 5.89 mm 封裝 / 箱體:F5 MicroCan 制造商:Maxim Integrated |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。