- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄97861 > DS1553WP-120 (DALLAS SEMICONDUCTOR) 0 TIMER(S), REAL TIME CLOCK, DMA34 PDF資料下載

參數(shù)資料

| 型號: | DS1553WP-120 |

| 廠商: | DALLAS SEMICONDUCTOR |

| 元件分類: | Timer or RTC |

| 英文描述: | 0 TIMER(S), REAL TIME CLOCK, DMA34 |

| 封裝: | POWERCAP MODULE-34 |

| 文件頁數(shù): | 16/19頁 |

| 文件大小: | 278K |

| 代理商: | DS1553WP-120 |

DS1553

6 of 19

SETTING THE CLOCK

The 8th bit, B7 of the Control Register is the write bit. Setting the write bit to a 1, like the read bit, halts

updates to the DS1553 (1FF8h-1FFFh) registers. After setting the write bit to a 1, RTC Registers can be

loaded with the desired RTC count (day, date, and time) in 24-hour BCD format. Setting the write bit to a

0 then transfers the values written to the internal RTC Registers and allows normal operation to resume.

CLOCK ACCURACY (DIP MODULE)

The DS1553 is guaranteed to keep time accuracy to within

±1 minute per month at 25°C. The RTC is

calibrated at the factory by Dallas Semiconductor using nonvolatile tuning elements and does not require

additional calibration. For this reason, methods of field clock calibration are not available and not

necessary. Clock accuracy is also effected by the electrical environment and caution should be taken to

place the RTC in the lowest level EMI section of the PCB layout.

For additional information see

application note 58.

CLOCK ACCURACY (POWERCAP MODULE)

The DS1553 and DS9034PCX are each individually tested for accuracy. Once mounted together, the

module is will typically keep time accuracy to within

±1.53 minutes per month (35 ppm) at 25°C. Clock

accuracy is effected by the electrical environment and caution should be taken to place the RTC in the

lowest level EMI section of the PCB layout. For additional information please see application note 58.

FREQUENCY TEST MODE

The DS1553 frequency test mode uses the open drain IRQ /FT output. With the oscillator running, the

IRQ

/FT output will toggle at 512 Hz when the FT bit is a 1, the Alarm Flag Enable bit (AE) is a 0, and

the Watchdog Steering bit (WDS) is a 1 or the Watchdog Register is reset (Register 1FF7h = 00h). The

IRQ

/FT output and the frequency test mode can be used as a measure of the actual frequency of the

32.768 kHz RTC oscillator. The IRQ /FT pin is an open drain output which requires a pullup resistor for

proper operation. The FT bit is cleared to a 0 on power-up.

USING THE CLOCK ALARM

The alarm settings and control for the DS1553 reside within Registers 1FF2h-1FF5h. Register 1FF6h

contains two alarm enable bits: Alarm Enable (AE) and Alarm in Backup Enable (ABE). The AE and

ABE bits must be set as described below for the IRQ /FT output to be activated for a matched alarm

condition.

The alarm can be programmed to activate on a specific day of the month or repeat every day, hour,

minute, or second. It can also be programmed to go off while the DS1553 is in the battery backed state of

operation to serve as a system wake-up. Alarm mask bits AM1-AM4 control the alarm mode. Table 3

shows the possible settings. Configurations not listed in the table default to the once per second mode to

notify the user of an incorrect alarm setting.

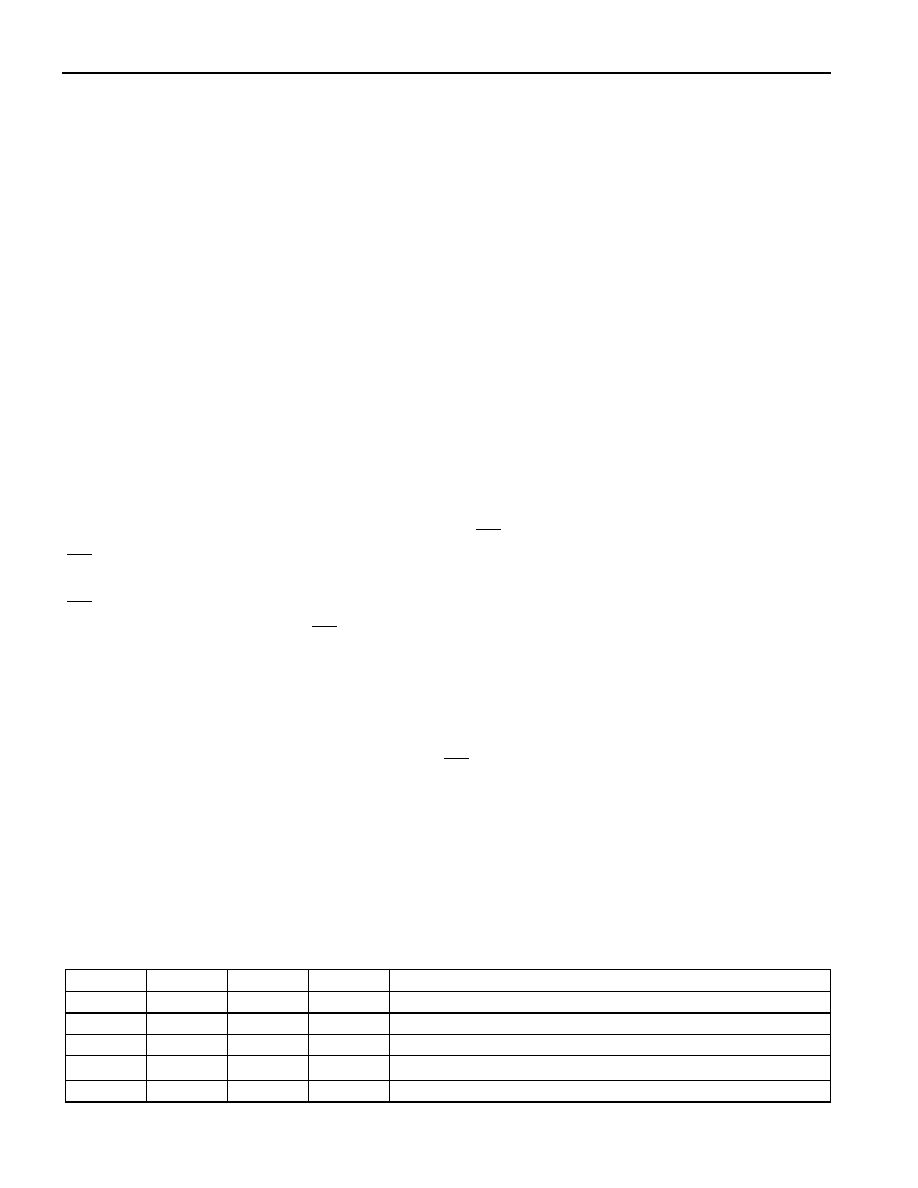

ALARM MASK BITS Table 3

AM4

AM3

AM2

AM1

ALARM RATE

1111

Once per second

1110

When seconds match

1100

When minutes and seconds match

1000

When hours, minutes, and seconds match

0000

When date, hours, minutes, and seconds match

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS1553-100 | 0 TIMER(S), REAL TIME CLOCK, DMA28 |

| DS1553W-120 | 0 TIMER(S), REAL TIME CLOCK, DMA28 |

| DS1553P-100 | 0 TIMER(S), REAL TIME CLOCK, DMA34 |

| DS1554-70 | 0 TIMER(S), REAL TIME CLOCK, PDMA32 |

| DS1554WP-120 | 0 TIMER(S), REAL TIME CLOCK |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS1553WP-120+ | 功能描述:實時時鐘 64kB NV RAM Timekeeper RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 總線接口:I2C 日期格式:DW:DM:M:Y 時間格式:HH:MM:SS RTC 存儲容量:64 B 電源電壓-最大:5.5 V 電源電壓-最小:1.8 V 最大工作溫度:+ 85 C 最小工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-8 封裝:Tube |

| DS1553WP-150 | 功能描述:實時時鐘 64kB NV RAM Timekeeper RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 總線接口:I2C 日期格式:DW:DM:M:Y 時間格式:HH:MM:SS RTC 存儲容量:64 B 電源電壓-最大:5.5 V 電源電壓-最小:1.8 V 最大工作溫度:+ 85 C 最小工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-8 封裝:Tube |

| DS1553WP-150+ | 功能描述:實時時鐘 64kB NV RAM Timekeeper RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 總線接口:I2C 日期格式:DW:DM:M:Y 時間格式:HH:MM:SS RTC 存儲容量:64 B 電源電壓-最大:5.5 V 電源電壓-最小:1.8 V 最大工作溫度:+ 85 C 最小工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-8 封裝:Tube |

| DS1554 | 制造商:DALLAS 制造商全稱:Dallas Semiconductor 功能描述:256K NV Y2KC Timekeeping RAM |

| DS1554-100 | 制造商:DALLAS 制造商全稱:Dallas Semiconductor 功能描述:256K NV Y2KC Timekeeping RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。