- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19029 > DC1525A-A (Linear Technology)BOARD DEMO 125MSPS LTC2175-14 PDF資料下載

參數(shù)資料

| 型號: | DC1525A-A |

| 廠商: | Linear Technology |

| 文件頁數(shù): | 16/34頁 |

| 文件大?。?/td> | 0K |

| 描述: | BOARD DEMO 125MSPS LTC2175-14 |

| 軟件下載: | QuikEval II System |

| 設(shè)計資源: | DC1525A Design Files |

| 標準包裝: | 1 |

| 系列: | * |

| 相關(guān)產(chǎn)品: | DC1371A-ND - BOARD USB DATA ACQUISITION HS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁

23

21754314fa

LTC2175-14/

LTC2174-14/LTC2173-14

applicaTions inForMaTion

DIGITAL OUTPUTS

The digital outputs of the LTC2175-14/LTC2174-14/

LTC2173-14 are serialized LVDS signals. Each channel

outputs two bits at a time (2-lane mode). At lower sam-

pling rates there is a one bit per channel option (1-lane

mode). The data can be serialized with 16, 14, or 12-bit

serialization (see timing diagrams for details). Note that

with 12-bit serialization the two LSBs are not available—

this mode is included for compatibility with the 12-bit

versions of these parts.

The output data should be latched on the rising and falling

edges of the data clock out (DCO). A data frame output

(FR) can be used to determine when the data from a new

conversion result begins. In the 2-lane, 14-bit serialization

mode, the frequency of the FR output is halved.

The maximum serial data rate for the data outputs is

1Gbps, so the maximum sample rate of the ADC will de-

pend on the serialization mode as well as the speed grade

of the ADC (see Table 1). The minimum sample rate for

all serialization modes is 5Msps.

By default the outputs are standard LVDS levels: 3.5mA

output current and a 1.25V output common mode volt-

age. An external 100 differential termination resistor

is required for each LVDS output pair. The termination

resistors should be located as close as possible to the

LVDS receiver.

The outputs are powered by OVDD and OGND which are

isolated from the A/D core power and ground.

Programmable LVDS Output Current

The default output driver current is 3.5mA. This current

can be adjusted by control register A2 in the serial pro-

gramming mode. Available current levels are 1.75mA,

2.1mA, 2.5mA, 3mA, 3.5mA, 4mA and 4.5mA. In the

parallel programming mode the SCK pin can select either

3.5mA or 1.75mA.

Optional LVDS Driver Internal Termination

In most cases using just an external 100 termination

resistor will give excellent LVDS signal integrity. In addi-

tion, an optional internal 100 termination resistor can

be enabled by serially programming mode control register

A2. The internal termination helps absorb any reflections

caused by imperfect termination at the receiver. When the

internal termination is enabled, the output driver current is

doubled to maintain the same output voltage swing. In the

parallel programming mode the SDO pin enables internal

termination. Internal termination should only be used with

1.75mA, 2.1mA or 2.5mA LVDS output current modes.

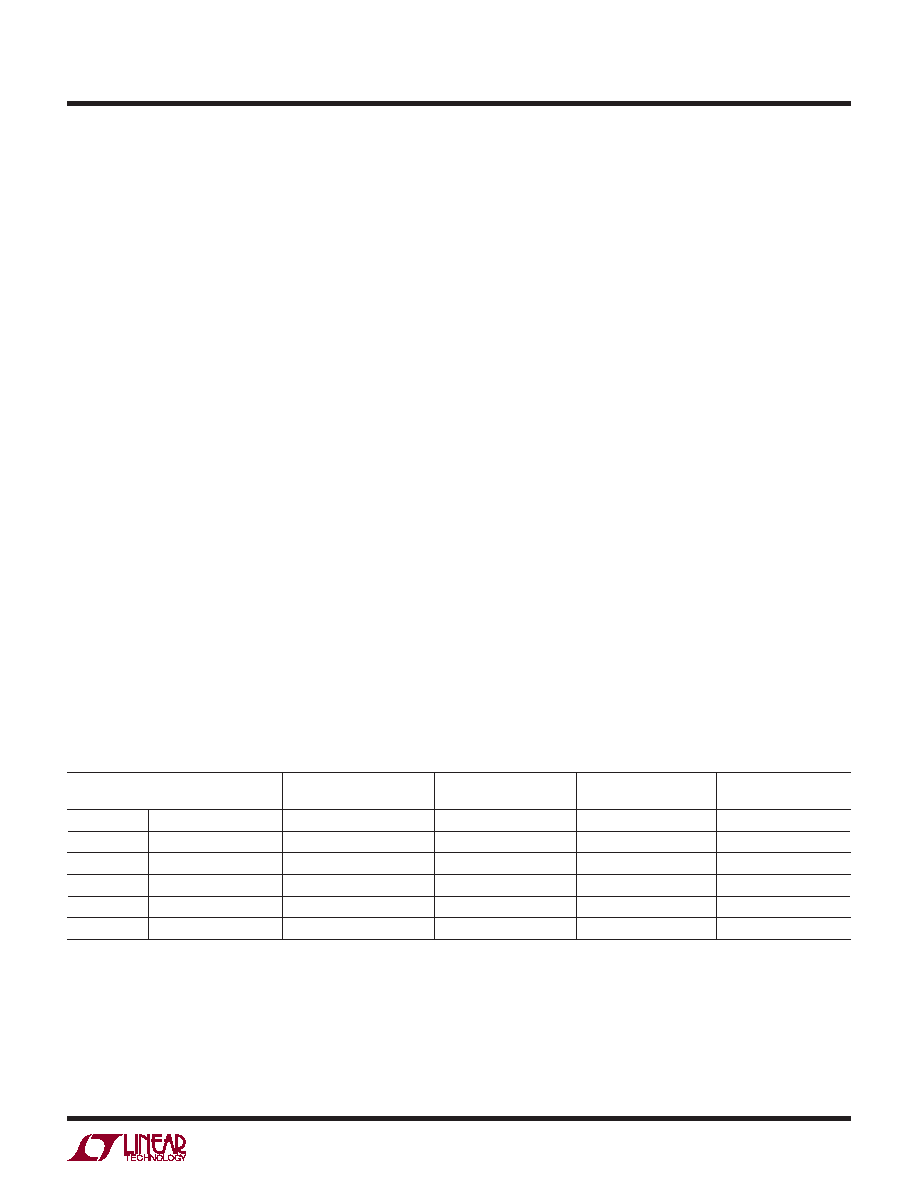

Table 1. Maximum Sampling Frequency for All Serialization Modes. Note That These Limits Are for the LTC2175-14. The Sampling

Frequency for the Slower Speed Grades Cannot Exceed 105MHz (LTC2174-14) or 80MHz (LTC2173-14).

SERIALIZATION MODE

MAXIMUM SAMPLING

FREQUENCY, fS (MHz)

DCO FREQUENCY

FR FREQUENCY

SERIAL DATA RATE

2-Lane

16-Bit Serialization

125

4 fS

fS

8 fS

2-Lane

14-Bit Serialization

125

3.5 fS

0.5 fS

7 fS

2-Lane

12-Bit Serialization

125

3 fS

fS

6 fS

1-Lane

16-Bit Serialization

62.5

8 fS

fS

16 fS

1-Lane

14-Bit Serialization

71.4

7 fS

fS

14 fS

1-Lane

12-Bit Serialization

83.3

6 fS

fS

12 fS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 48ESB | LAMP INCAND T-2 TELE SLIDE 48V |

| CQM1-TC201 | 4 LOOP THERMOCPLE IN NPN OUT |

| 35A1 | LAMP INCAND T-2 TELE SLIDE 35V |

| 24B1 | LAMP INCAND T-2 TELE SLIDE 24V |

| 8098 | LAMP INCAND 3MM STD BI-PIN 14V |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DC1525A-B | 功能描述:BOARD DEMO 105MSPS LTC2174-14 RoHS:是 類別:未定義的類別 >> 其它 系列:* 標準包裝:1 系列:* 其它名稱:MS305720A |

| DC1525A-C | 功能描述:BOARD DEMO 80MSPS LTC2173-14 RoHS:是 類別:未定義的類別 >> 其它 系列:* 標準包裝:1 系列:* 其它名稱:MS305720A |

| DC1525A-D | 功能描述:BOARD DEMO 65MSPS LTC2172-14 RoHS:是 類別:未定義的類別 >> 其它 系列:* 標準包裝:1 系列:* 其它名稱:MS305720A |

| DC1525A-E | 功能描述:BOARD DEMO 40MSPS LTC2171-14 RoHS:是 類別:未定義的類別 >> 其它 系列:* 標準包裝:1 系列:* 其它名稱:MS305720A |

| DC1525A-F | 功能描述:BOARD DEMO 25MSPS LTC2170-14 RoHS:是 類別:未定義的類別 >> 其它 系列:* 標準包裝:1 系列:* 其它名稱:MS305720A |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。