- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄17026 > CDB5368 (Cirrus Logic Inc)BOARD EVAL FOR CS5368 192KHZ ADC PDF資料下載

參數(shù)資料

| 型號(hào): | CDB5368 |

| 廠商: | Cirrus Logic Inc |

| 文件頁(yè)數(shù): | 7/19頁(yè) |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR CS5368 192KHZ ADC |

| 標(biāo)準(zhǔn)包裝: | 1 |

| ADC 的數(shù)量: | 1 |

| 位數(shù): | 24 |

| 采樣率(每秒): | 192k |

| 數(shù)據(jù)接口: | 串行 |

| 輸入范圍: | ±0.3 V |

| 工作溫度: | -40°C ~ 85°C |

| 已用 IC / 零件: | CS5368 |

| 已供物品: | 板,線纜 |

| 產(chǎn)品目錄頁(yè)面: | 756 (CN2011-ZH PDF) |

| 相關(guān)產(chǎn)品: | CS5368-DQZ-ND - IC ADC 8CH 114DB 216KHZ 48-LQFP CS5368-CQZR-ND - IC ADC 8CH 114DB 216KHZ 48-LQFP 598-1090-ND - IC ADC 8CH 114DB 216KHZ 48-LQFP |

| 其它名稱: | 598-1157 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)

DS624F4

15

CS5368

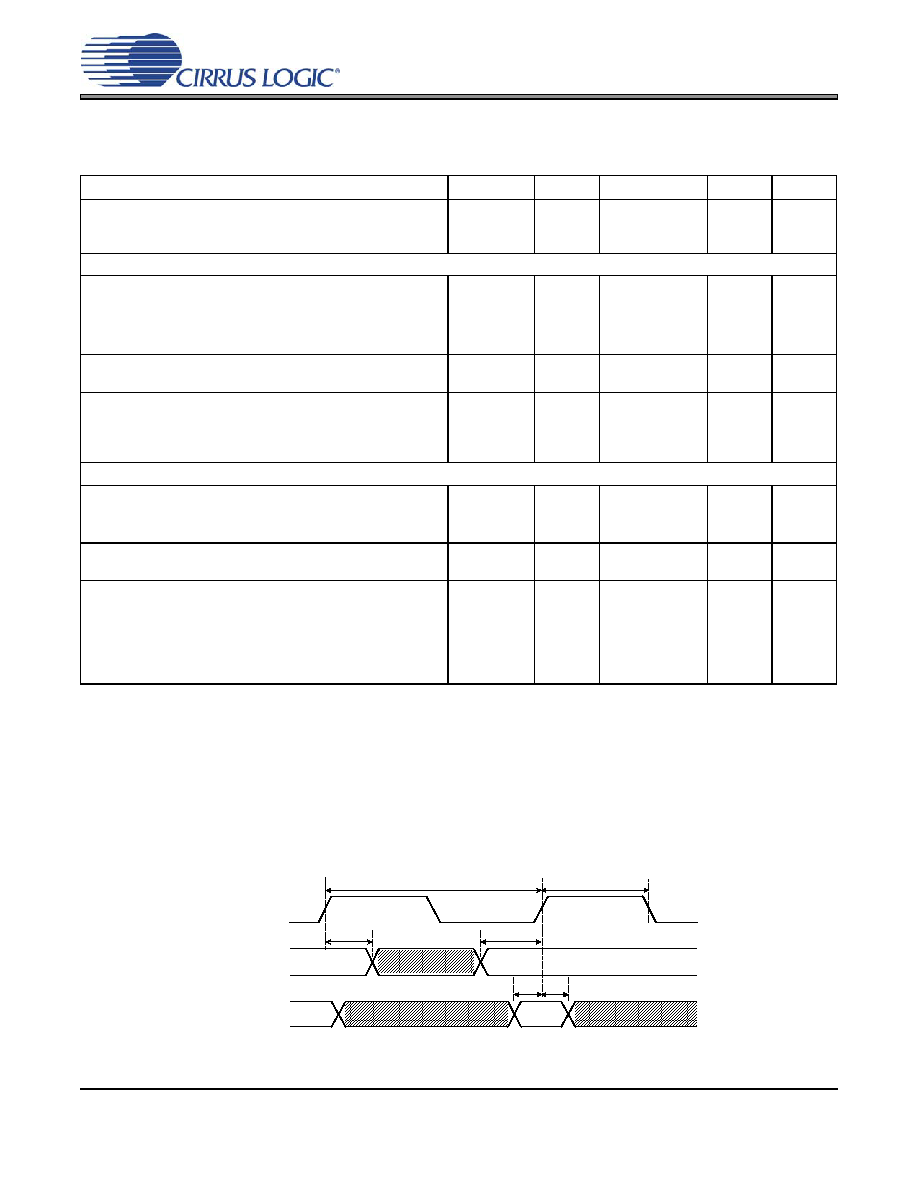

SERIAL AUDIO INTERFACE - IS/LJ TIMING

The serial audio port is a three-pin interface consisting of SCLK, LRCK and SDOUT.

Logic "0" = GND = 0 V; Logic "1" = VLS; CL = 20 pF, timing threshold is 50% of VLS.

Notes:

1.

Duty cycle of generated SCLK depends on duty cycle of received MCLK as specified under “System

2.

CLKMODE functionality described in Section 4.6.3

3.

In Slave Mode, the SCLK/LRCK ratio can be set according to preference. However, chip performance

is guaranteed only when using the ratios in Section 4.7 Master and Slave Clock Frequencies on page

Figure 3. IS/LJ Timing

Parameter

Symbol

Min

Typ

Max

Unit

Sample Rates

Single-Speed Mode

Double-Speed Mode

Quad-Speed Mode

-

2

54

108

-

54

108

216

kHz

Master Mode

SCLK Frequency

SCLK Period

1/(64*216 kHz)

SCLK Duty Cycle (Note 1)

(CLKMODE = 0)(Note 2)

(CLKMODE = 1)(Note 2)

-

tPERIOD

tHIGH

64*Fs

72.3

40

28

-

50

33

64*Fs

-

60

38

Hz

ns

%

LRCK setup

before SCLK rising

LRCK hold

after SCLK rising

tSETUP1

tHOLD1

20

--

ns

SDOUT setup

before SCLK rising

SDOUT hold

after SCLK rising (VLS = 1.8 V)

after SCLK rising (VLS = 3.3 V)

after SCLK rising (VLS = 5 V)

tSETUP2

tHOLD2

10

20

10

5

--

ns

Slave Mode

SCLK Frequency (Note 3)

SCLK Period

1/(64*216 kHz)

SCLK Duty Cycle

-

tPERIOD

tHIGH

-

72.3

28

64*Fs

-

65

Hz

ns

%

LRCK setup

before SCLK rising

LRCK hold

after SCLK rising

tSETUP1

tHOLD1

20

--

ns

SDOUT setup

before SCLK rising (VLS = 1.8 V)

before SCLK rising (VLS = 3.3 V)

before SCLK rising (VLS = 5 V)

SDOUT hold

after SCLK rising (VLS = 1.8 V)

after SCLK rising (VLS = 3.3 V)

after SCLK rising (VLS = 5 V)

tSETUP2

tHOLD2

4

10

20

10

5

--

ns

LRCK

SDOUT

SCLK

data

channel

data

t

HOLD2

t

SET UP2

t

HOLD1

t

SET UP1

t

PERIOD

t

HIGH

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VE-J1B-EY | CONVERTER MOD DC/DC 95V 50W |

| VE-J14-EY | CONVERTER MOD DC/DC 48V 50W |

| EVAL-AD977ACB | BOARD EVAL FOR AD977A |

| VE-BWZ-EY | CONVERTER MOD DC/DC 2V 20W |

| VE-BWZ-EX | CONVERTER MOD DC/DC 2V 30W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CDB5374 | 功能描述:音頻 IC 開發(fā)工具 2-Ch DS Modulator & Hydrophone Demo Brd RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Kits 類型:Audio Amplifiers 工具用于評(píng)估:TAS5614L 工作電源電壓:12 V to 38 V |

| CDB5376 | 功能描述:音頻 IC 開發(fā)工具 Eval Bd LP Mult-Ch Decimation Filter RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Kits 類型:Audio Amplifiers 工具用于評(píng)估:TAS5614L 工作電源電壓:12 V to 38 V |

| CDB5376Z | 制造商:Cirrus Logic 功能描述:PB-FREE EVAL BD LOW-POWER, MULTICH DECIMATION FILTER - Bulk |

| CDB5378 | 功能描述:音頻 IC 開發(fā)工具 Eval Bd LP Mult-Ch Decimation Filter RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Kits 類型:Audio Amplifiers 工具用于評(píng)估:TAS5614L 工作電源電壓:12 V to 38 V |

| CDB5378Z | 制造商:Cirrus Logic 功能描述:PB-FREE EVAL BD LOW-POWER, MULTICH DECIMATION FILTER - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。