- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄166591 > BU-61864F4-140Y (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 PDF資料下載

參數(shù)資料

| 型號: | BU-61864F4-140Y |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| 封裝: | 25.40 X 25.40 MM, 3.94 MM HEIGHT, CERAMIC, FP-72 |

| 文件頁數(shù): | 27/60頁 |

| 文件大小: | 457K |

| 代理商: | BU-61864F4-140Y |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

33

Data Device Corporation

www.ddc-web.com

BU-6174X/6184X/6186X

F-10/02-300

15

13

0

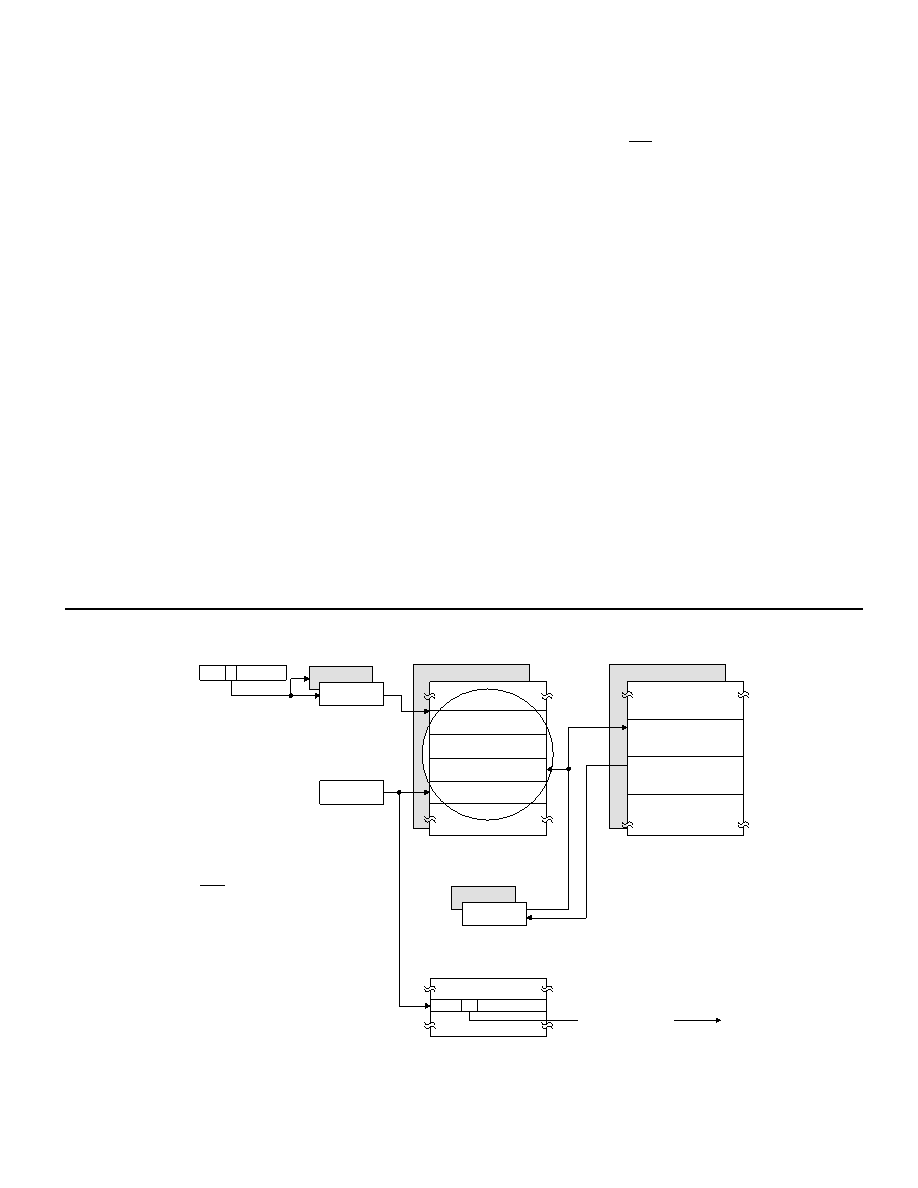

BLOCK STATUS WORD

TIME TAG WORD

DATA BLOCK POINTER

RECEIVED COMMAND

WORD

CONFIGURATION

REGISTER #1

MONITOR COMMAND

STACK POINTERS

MONITOR

COMMAND STACKS

CURRENT

AREA B/A

MONITOR DATA

STACKS

MONITOR DATA

BLOCK #N + 1

MONITOR DATA

BLOCK #N

CURRENT

COMMAND WORD

MONITOR DATA

STACK POINTERS

IF THIS BIT IS "0" (NOT SELECTED)

NO WORDS ARE STORED IN EITHER

THE COMMAND STACK OR DATA STACK.

IN ADDITION, THE COMMAND AND DATA

STACK POINTERS WILL NOT BE UPDATED.

NOTE

SELECTIVE MONITOR

LOOKUP TABLES

SELECTIVE MONITOR

ENABLE

(SEE NOTE)

OFFSET BASED ON

RTA4-RTA0, T/R, SA4

FIGURE 11. SELECTIVE MESSAGE MONITOR MEMORY MANAGEMENT

TIME TAG

The

Enhanced

Mini-ACE/-ACE

includes

an

internal

read/writable Time Tag Register. This register is a CPU

read/writable 16-bit counter with a programmable resolution of

either 2, 4, 8, 16, 32, or 64 s per LSB. Another option allows

software controlled incrementing of the Time Tag Register. This

supports self-test for the Time Tag Register. For each message

processed, the value of the Time Tag Register is loaded into the

second location of the respective descriptor stack entry ("TIME

TAG WORD") for both the BC and RT modes.

The functionality involving the Time Tag Register that's compati-

ble with ACE/Mini-ACE (Plus) includes: the capability to issue an

interrupt request and set a bit in the Interrupt Status Register

when the Time Tag Register rolls over FFFF to 0000; for RT

mode, the capability to automatically clear the Time Tag Register

following reception of a Synchronize (without data) mode com-

mand, or to load the Time Tag Register following a Synchronize

(with data) mode command.

Additional time tag features supported by the Enhanced Mini-

ACE/-ACE include the capability for the BC to transmit the con-

tents of the Time Tag Register as the data word for a

Synchronize (with data) mode command; the capability for the

RT to "filter" the data word for the Synchronize with data mode

command, by only loading the Time Tag Register if the LSB of

the received data word is "0"; an instruction enabling the BC

Message Sequence Control engine to load the Time Tag

Register with a specified value; and an instruction enabling the

BC Message Sequence Control engine to write the value of the

Time Tag Register to the General Purpose Queue.

INTERRUPTS

The Enhanced Mini-ACE/-ACE series terminals provide many

programmable options for interrupt generation and handling.

The interrupt output pin (INT) has three software programmable

modes of operation: a pulse, a level output cleared under soft-

ware control, or a level output automatically cleared following a

read of the Interrupt Status Register (#1 or #2).

Individual interrupts are enabled by the two Interrupt Mask

Registers. The host processor may determine the cause of the

interrupt by reading the two Interrupt Status Registers, which

provide the current state of interrupt events and conditions. The

Interrupt Status Registers may be updated in two ways. In one

interrupt handling mode, a particular bit in Interrupt Status

Register #1 or #2 will be updated only if the event occurs and the

corresponding bit in Interrupt Mask Register #1 or #2 is enabled.

In the enhanced interrupt handling mode, a particular bit in one

of the Interrupt Status Registers will be updated if the event/con-

dition occurs regardless of the value of the corresponding

Interrupt Mask Register bit. In either case, the respective

Interrupt Mask Register (#1 or #2) bit is used to enable an inter-

rupt for a particular event/condition.

The Enhanced Mini-ACE/-ACE supports all the interrupt events

from ACE/Mini-ACE (Plus), including RAM Parity Error, Transmitter

Timeout, BC/RT Command Stack Rollover, MT Command Stack

and Data Stack Rollover, Handshake Error, BC Retry, RT Address

Parity Error, Time Tag Rollover, RT Circular Buffer Rollover, BC

Message, RT Subaddress, BC End-of-Frame, Format Error, BC

Status Set, RT Mode Code, MT Trigger, and End-of-Message.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BU-61864G3-112Z | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61864G3-180K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61865F3-142Z | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61865F4-130Z | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61865G3-112W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BU-61864G3-100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| BU-61864G3-110 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| BU-61864G4-100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| BU-61864G4-110 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| BU-61864G4-200 | 制造商:DDC 功能描述:MIL-STD-1553/ARINC BUS CONTROLLER/RTU, 72 Pin, QFP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。