- 您現在的位置:買賣IC網 > PDF目錄166580 > BU-61845G4-140L (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 PDF資料下載

參數資料

| 型號: | BU-61845G4-140L |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| 封裝: | 25.40 X 25.40 MM, 2.54 MM HEIGHT, CERAMIC, QFP-72 |

| 文件頁數: | 33/60頁 |

| 文件大小: | 457K |

| 代理商: | BU-61845G4-140L |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁當前第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

39

Data Device Corporation

www.ddc-web.com

BU-6174X/6184X/6186X

F-10/02-300

(uncontended access @ 16 MHz)

112

ns

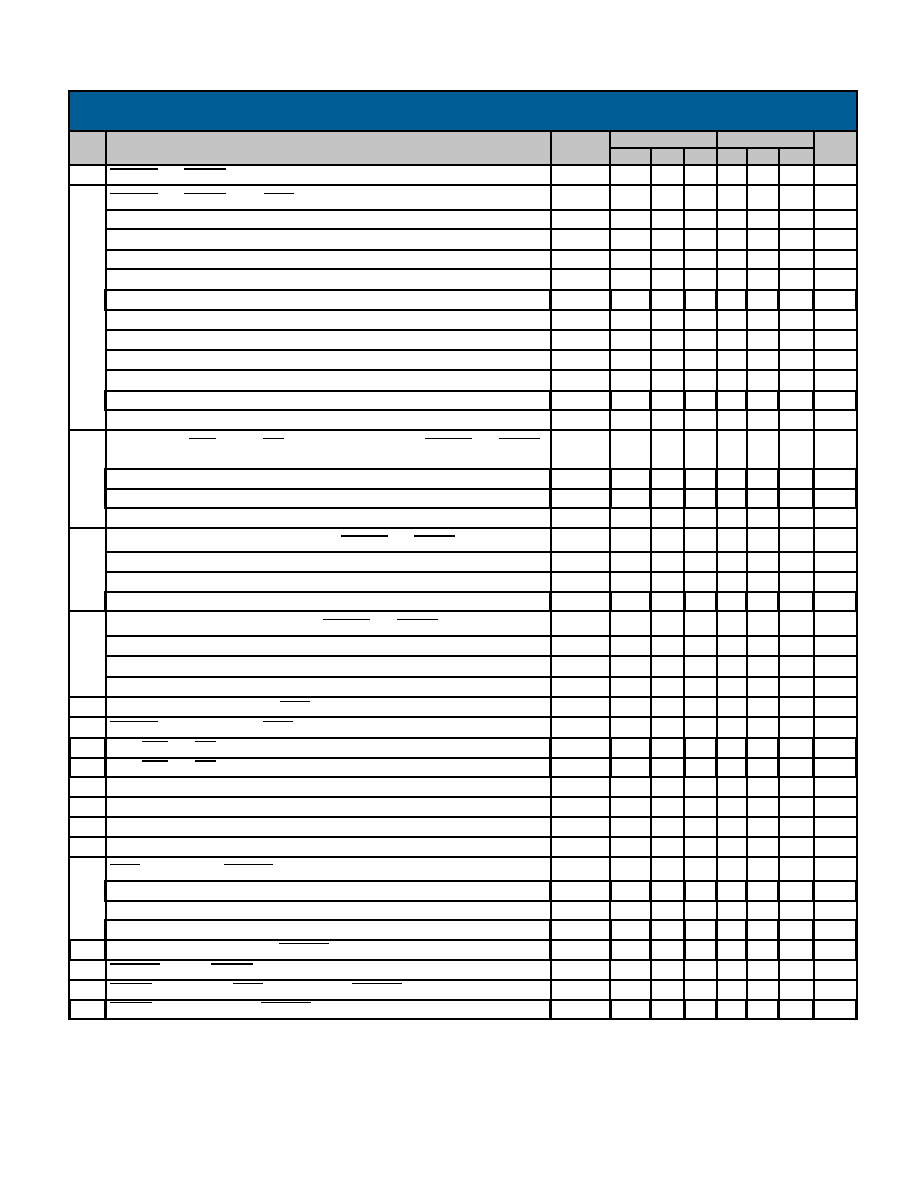

TABLE FOR FIGURE 14. CPU WRITING RAM OR REGISTERS

(SHOWN FOR 16-BIT, BUFFERED, NONZERO WAIT MODE)

3.3V LOGIC

5V LOGIC

@ 16 MHz

t1

SELECT and STRBD low setup time prior to clock rising edge

10

ns

50

t2

SELECT and STRBD low to IOEN low (uncontended access @ 20 MHz)

100

ns

(contended access, with ENHANCED CPU ACCESS = “0” @ 20 MHz)

3.6

s

Time for MEM/REG and RD/WR to become valid following SELECT and STRBD

low(@ 20 MHz)

15

ns

@ 16 MHz

21

ns

45

Time for Address to become valid following SELECT and STRBD low (@ 20 MHz)

17

ns

Time for data to become valid following SELECT and STRBD low (@ 20 MHz)

37

ns

t7

SELECT hold time following IOEN falling

0

ns

@ 12 MHz

t10

Address valid setup time prior to CLOCK IN rising edge

30

ns

IOEN falling delay to READYD falling @ 20 MHz

85

100

115

ns

t12

Address valid hold time prior to CLOCK IN rising edge

30

ns

70

85

100

115

6, 9

@ 16 MHz

ns

t8

MEM/REG, RD/WR setup time prior to CLOCK IN falling edge

10

ns

110

125

140

ns

110 125

140

6, 9

@ 12 MHz

152

167

65

t11

Data valid setup time prior to CLOCK IN rising edge

10

ns

t9

MEM/REG, RD/WR setup time following CLOCK IN falling edge

30

ns

t5

(contended access, with ENHANCED CPU ACCESS = “1” @ 20 MHz)

350

ns

@ 10 MHz

@ 16 MHz

30

ns

t6

CLOCK IN rising edge delay to IOEN falling edge

40

ns

87

t13

Data valid hold time following CLOCK IN rising edge

10

ns

t15

CLOCK IN rising edge delay to READYD falling

40

ns

t16

READYD falling to STRBD rising release time

∞

ns

82

t17

STRBD rising delay to IOEN rising edge and READYD rising edge

30

ns

t18

STRBD high hold time from READYD rising

10

ns

182

ns

152 167

182

6, 9

t14

@ 10 MHz

185

200

215

ns

185 200

215

6, 9

@ 12 MHz

50

ns

t4

@ 10 MHz

67

ns

@ 12 MHz

32

ns

t3

@ 10 MHz

40

ns

(contended access, with ENHANCED CPU ACCESS = “0” @ 12 MHz)

6.0

s

(contended access, with ENHANCED CPU ACCESS = “0” @ 16 MHz)

4.6

s

(contended access, with ENHANCED CPU ACCESS = “1” @ 16 MHz)

425

ns

(uncontended access @ 12 MHz)

133

ns

(contended access, with ENHANCED CPU ACCESS = “1” @ 10 MHz)

650

ns

(contended access, with ENHANCED CPU ACCESS = “1” @ 12 MHz)

550

ns

(uncontended access @ 10 MHz)

150

ns

(contended access, with ENHANCED CPU ACCESS = “0” @ 10 MHz)

7.2

s

117

2, 6

2, 10

NOTES

15

105

2.2

10

16

12

32

0

35

30

15

35

355

25

40

15

40

∞

40

10

45

62

27

35

3.7

2.8

430

138

655

555

155

4.4

REF

DESCRIPTION

MIN

TYP MAX

UNITS

MIN TYP MAX

2, 6

3, 4, 5, 7

2

7, 8

7, 8, 9

3, 4, 5, 7

2, 6

6

9

6

3, 4, 5, 7

2, 6

相關PDF資料 |

PDF描述 |

|---|---|

| BU-61845G4-140Q | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61845G4-140S | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61845G4-140Y | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61845G4-150Q | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61845G4-150 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| BU-61860B3NEW | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |μ-ACE (Micro-ACE?) |

| BU-61864 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |Enhanced Mini-ACE? |

| BU-61864F3-100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| BU-61864F3-110 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| BU-61864F4-100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

發(fā)布緊急采購,3分鐘左右您將得到回復。