2

Data

De

vice

Cor

por

ation

www

.d

dc-web.com

B

U-6174X/6184X/6186X

F-10/02-300

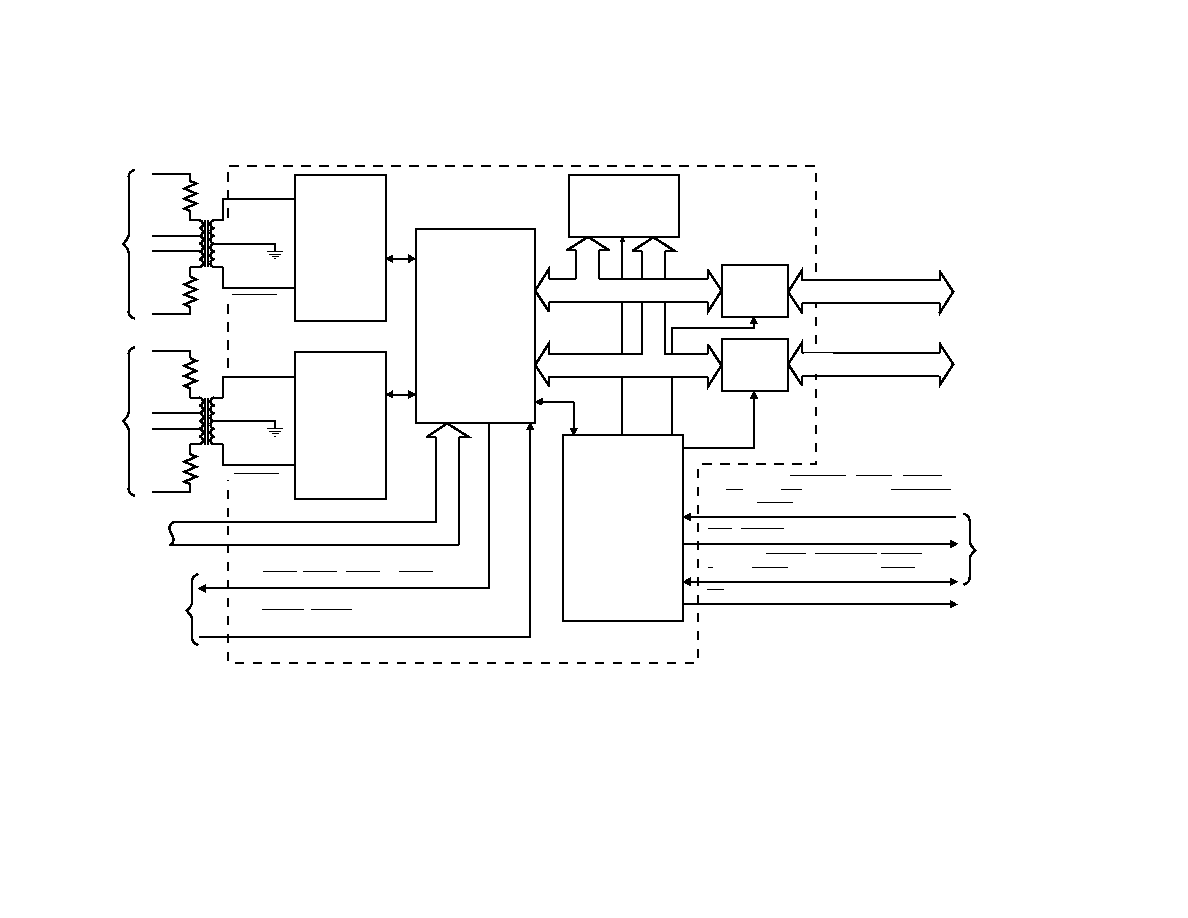

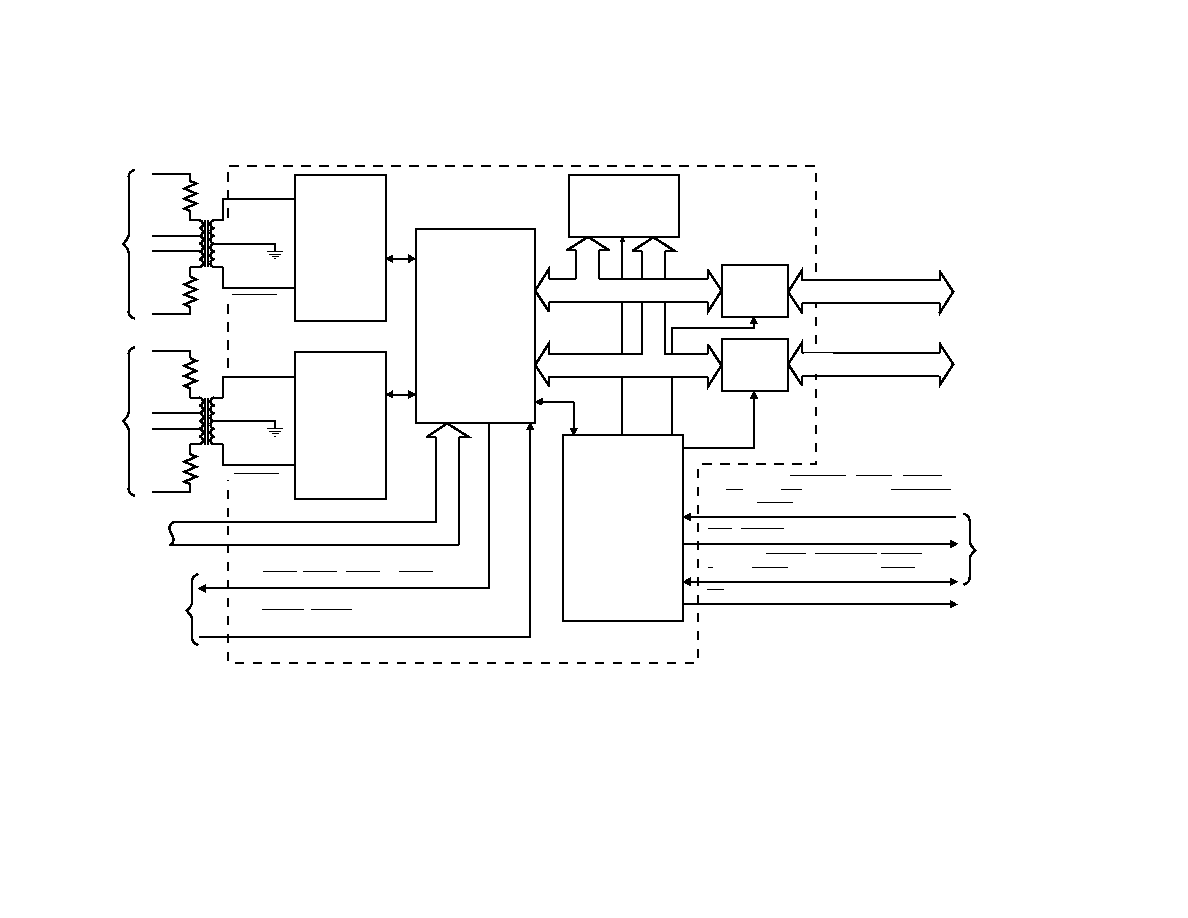

FIGURE 1. ENHANCED MINIATURE ADVANCED COMMUNICATIONS ENGINE BLOCK DIAGRAM

TRANSCEIVER

A

CH. A

TRANSCEIVER

B

CH. B

DUAL

ENCODER/DECODER,

MULTIPROTOCOL

AND

MEMORY

MANAGEMENT

RT ADDRESS

SHARED

RAM (1)

ADDRESS BUS

PROCESSOR

AND

MEMORY

INTERFACE

LOGIC

DATA BUS

D15-D0

A15-A0

DATA

BUFFERS

ADDRESS

BUFFERS

PROCESSOR

DATA BUS

PROCESSOR

ADDRESS BUS

MISCELLANEOUS

INCMD/MCRST, INCMD(2), MCRST(2)

CLK_IN, TAG_CLK(2),

MSTCLR, SSFLAG/EXT_TRG, TX-INH_A, TX-INH_B,

UPADDREN, RSBITEN(2)

RTAD4-RTAD0, RTADP

TRANSPARENT/BUFFERED, STRBD, SELECT,

RD/WR, MEM/REG, TRIGGER_SEL/MEMENA-IN,

MSB/LSB/DTGRT

IOEN, READYD

ADDR_LAT/MEMOE, ZERO_WAIT/MEMWR,

8/16-BIT/DTREQ, POLARITY_SEL/DTACK

INT

PROCESSOR

AND

MEMORY

CONTROL

INTERRUPT

REQUEST

TX/RX_A

TX/RX_B

NOTE 1: See Ordering Information for Available Memory Options.

NOTE 2: Indicates signals brought out only on -ACE (BGA package) version.