- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄223461 > BU-61703G4-152L (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 PDF資料下載

參數(shù)資料

| 型號: | BU-61703G4-152L |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 |

| 封裝: | 1 X 1 INCH, GULL WING, PACKAGE-72 |

| 文件頁數(shù): | 52/52頁 |

| 文件大小: | 367K |

| 代理商: | BU-61703G4-152L |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁當前第52頁

9

MIL-STD-1553A*/B

(-B is logic "1", or the

default).

POWER-UP SELF-

TEST ENABLE

BURST MODE

SUBADDRESS 30

WRAPAROUND

RTFAIL-to-TERMINAL

FLAG AUTO-WRAP

RT GOES ONLINE IF

SELF-TEST FAILS

FUNCTION

In MIL-STD-1553B mode, subaddress

31 is a mode code subaddress, and

mode codes are implemented in full

accordance with MIL-STD-1553B. In

MIL-STD-1553A mode, subaddress 31

is a non-mode code subaddress, and no

data words are transmitted or anticipat-

ed to be received for mode code mes-

sages.

If enabled, the SSRT will perform self-

test following the rising edge of MST-

CLR*.

0

Enables burst mode (using the internal

FIFO) for received data words. In burst

mode, for a receive message, all data

words are transferred to the external

system in a contiguous burst following

reception of the last data word.

1

Subaddress 30 wraparound is enabled.

That is, the data words for a receive

message to subaddress 30 are stored in

the internal FIFO, and not transferred to

the external system. For a subsequent

transmit message to subaddress 30, the

transmitted data words are read from

the internal FIFO, rather than from the

external system.

2

If the loop test fails for a particular mes-

sage, the Terminal flag bit will be set in

the SSRT's status response for the sub-

sequent non-broadcast message.

4

If logic "0", the RT will become enabled

only if the self-test passes. If auto-config

is not used, or if this bit is logic "1", or if

the power-up self-test passes, then the

RT will go online following self-test.

5

DESCRIPTION

BIT

3

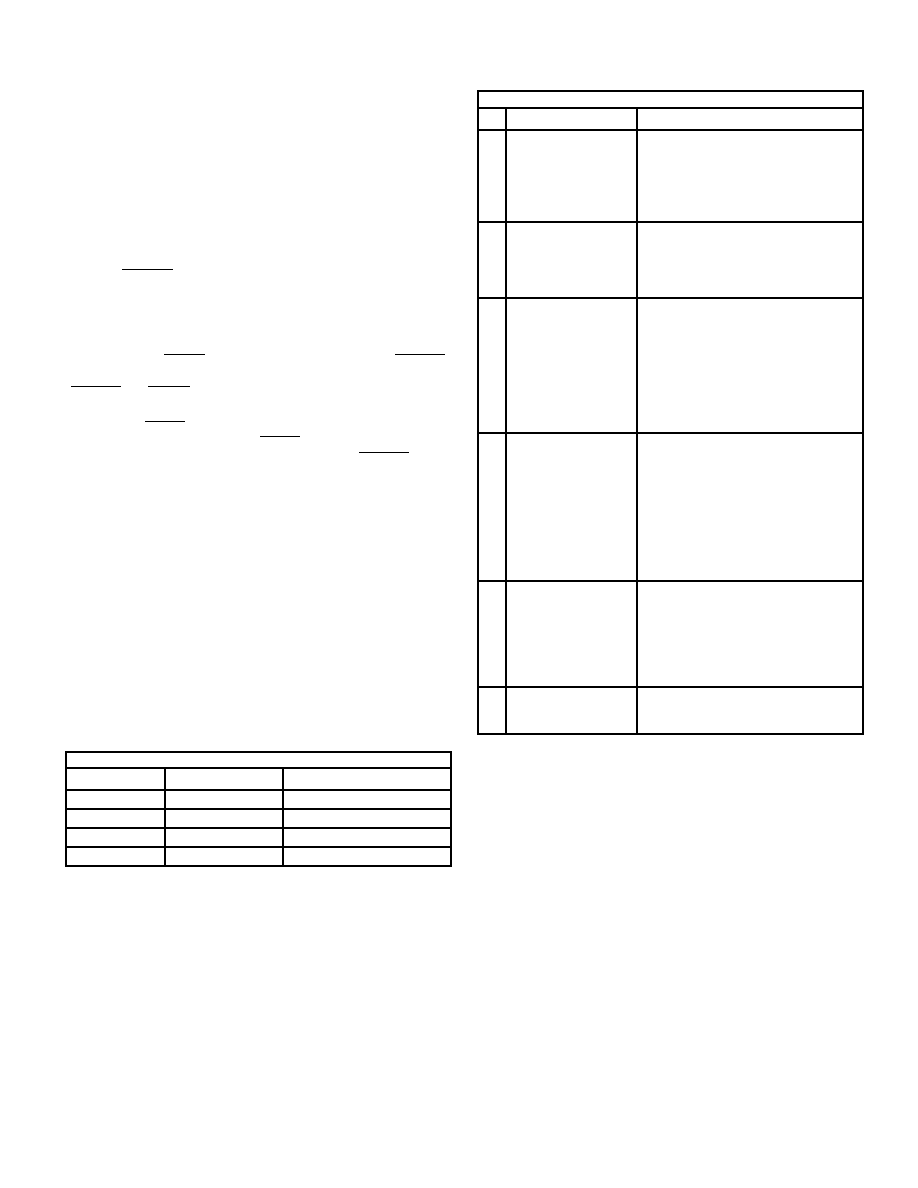

TABLE 2. AUTO-CONFIGURATION PARAMETERS

0

1

0

CLK_SEL_0

12 MHz

16 MHz

1

20 MHz

0

10 MHz

0

CLOCK FREQUENCY

CLK_SEL_1

1

TABLE 3. CLOCK FREQUENCY SELECTION

CLOCK INPUT

The SSRT may be operated from one of four clock frequencies:

10, 12, 16, or 20 MHz. The selected clock frequency must be des-

ignated by means of the input signals CLK_SEL_1 and

CLK_SEL_0, as shown in Table 3.

AUTO-CONFIGURATION

The SSRT includes an auto-configuration feature, which allows

various optional features to be enabled or disabled. Auto-configu-

ration may be enabled or disabled by means of the input signal

. If

is connected to logic "1", then the

auto-configure option is disabled, and the six configuration para-

meters revert to their default values.

Note that the default condition for each configuration para-

meter is enabled (for the MIL-STD-1553A/B protocol selection, -

1553B is the default).

If

is connected to logic "0", then the configuration

parameters are transferred over D5-D0 by means of a DMA read

data transfer. The transfer occurs during the time that the

RTACTIVE

and

outputs are logic "0", following

transitioning from logic "0" to logic "1" and a successful

-to-

handshake.

Note that if

is hardwired to logic "0", the handshake

process is not necessary (i.e.,

and RTACTIVE will both

be asserted to logic "0" one clock cycle following

).

Each of the configuration parameters is enabled if the SSRT

reads a value of logic "1" for the respective data bit.

The auto-configuration parameters are defined by Table 2.

The timing signals pertaining to Auto-Configuration mode are

illustrated in FIGURE 12.

REQ

_

DT

DTACK

DTGRT

REQ

_

DT

MSTCLR

DTACK

CFG

_

AUTO

CFG

_

AUTO

CFG

_

AUTO

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BU-61703G4-152Y | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 |

| BU-61703G4-152 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 |

| BU-61703G4-162Q | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 |

| BU-61703G4-162S | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 |

| BU-61703G4-172K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BU-61705 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |Simple System RT |

| BU-61740B3NEW | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |μ-ACE (Micro-ACE?) |

| BU-61743 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |Enhanced Mini-ACE? |

| BU-61743F3-100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| BU-61743F3-110 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

發(fā)布緊急采購,3分鐘左右您將得到回復。