- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄166494 > BU-61582D2-491K (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 PDF資料下載

參數(shù)資料

| 型號: | BU-61582D2-491K |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| 封裝: | CERAMIC, DIP-70 |

| 文件頁數(shù): | 11/48頁 |

| 文件大?。?/td> | 378K |

| 代理商: | BU-61582D2-491K |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

19

Data Device Corporation

www.ddc-web.com

BU-61582

G-08/02-250

Upon completion of the message, provided that the message

was valid and Subaddress Double Buffering is enabled, the BU-

61582 will automatically switch the “active” and “inactive” blocks

for the respective subaddress. The SP’ACE accomplishes this by

toggling bit 5 of the subaddress’s Lookup Table Pointer and

rewriting the pointer. As a result, the most recent valid block of

received Data Words will always be readily accessible to the host

processor.

As a means of ensuring data consistency, the host processor is

able to reliably access the most recent valid, received Data Word

block by performing the following sequence:

(1) Disable the double buffering for the respective subaddress by

the Subaddress Control Word. That is, temporarily switch the

subaddress’s memory management scheme to the Single

Message mode.

(2) Read the current value of the receive (or broadcast) subad-

dress’s Lookup Table pointer. This points to the current “active”

Data Word block. By inverting bit 5 of this pointer value, it is pos-

sible to locate the start of the “inactive” Data Word block. This

block will contain the Data Words received during the most

recent valid message to the subaddress.

(3) Read out the words from the “inactive” (most recent) Data

Word Block.

(4) Re-enable the Double Buffering mode for the respective sub-

address by the Subaddress Control Word.

RT INTERRUPTS

As in BC mode, the BU-61582 RT provides many maskable

interrupts. RT interrupt conditions include End of (every)

Message, Message Error, Selected Subaddress (Subaddress

Control Word) Interrupt, Circular Buffer Rollover, Selected Mode

Code Interrupt, and Stack Rollover.

DESCRIPTOR STACK

At the beginning and end of each message, the BU-61582 RT

stores a four-word message descriptor in the active area stack.

The RT stack size is programmable, with choices of 256, 512,

1024, and 2048 words. FIGURES 5, 6, and 7 show the four

words: Block Status Word, Time Tag Word, Data Block Pointer,

and the 1553 received Command Word. The RT Block Status

Word includes indications of message in-progress or message

complete, bus channel, RT-to-RT transfer and RT-to-RT transfer

errors, message format error, loop test (self-test) failure, circular

buffer rollover, illegal command, and other error conditions.

TABLE 24 shows the bit mapping of the RT Block Status Word.

As in BC mode, the Time Tag Word stores the current contents

of the BU-61582’s read/writable Time Tag Register. The resolu-

tion of the Time Tag Register is programmable from among 2, 4,

8, 16, 32, and 64 s/LSB. Also, incrementing of the Time Tag

counter may be from an external clock source or via software

command.

The SP’ACE stores the contents of the accessed Lookup Table

location for the current message, indicating the starting location

of the Data Word block, as the Data Block Pointer. This serves

as a convenience in locating stored message data blocks. The

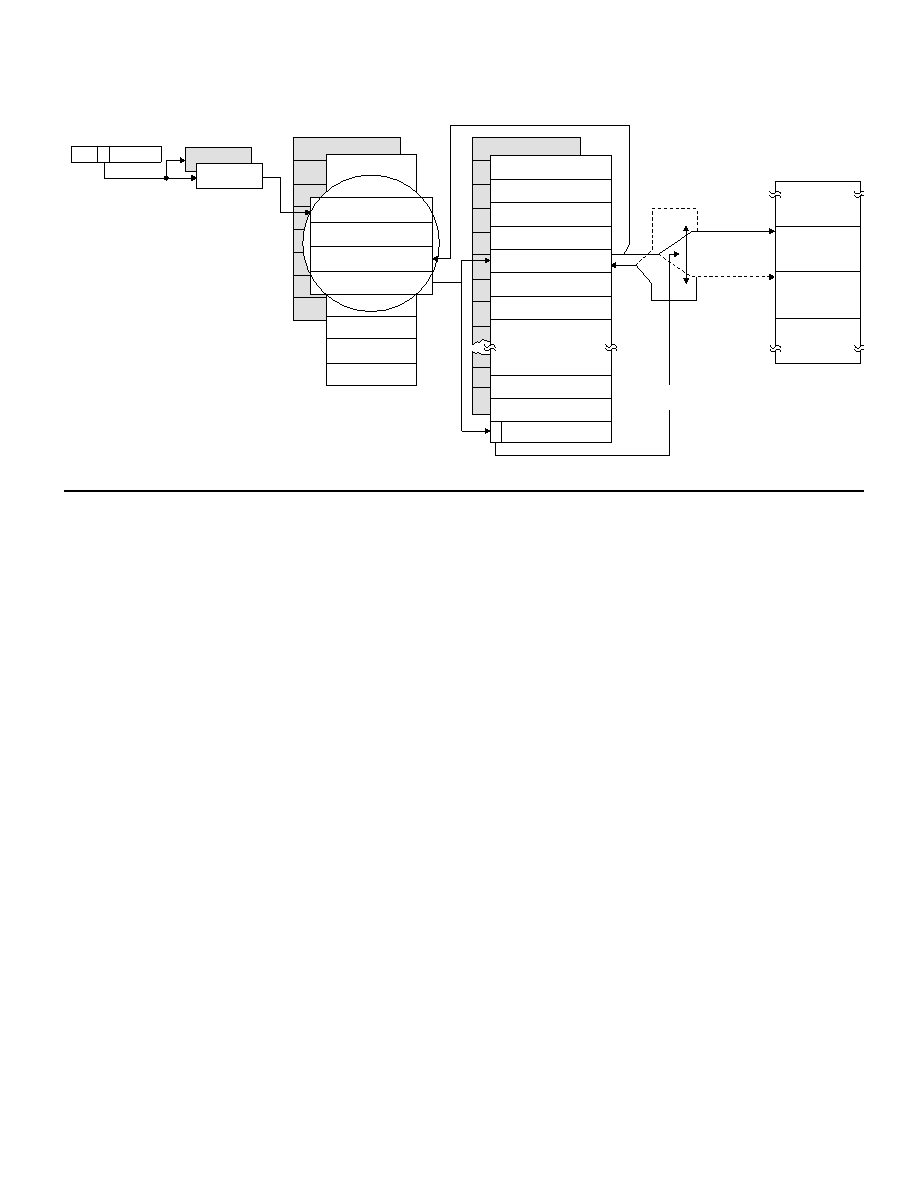

FIGURE 7. RT MEMORY MANAGEMENT: SUBADDRESS DOUBLE BUFFERING MODE

15

13

0

BLOCK STATUS WORD

TIME TAG WORD

DATA BLOCK POINTER

RECEIVED COMMAND

WORD

CONFIGURATION

REGISTER

STACK

POINTERS

DESCRIPTOR

STACK

CURRENT

AREA B/A

DATA

BLOCKS

DATA

BLOCK 1

DATA

BLOCK 0

X..X 0 YYYYY

X..X 1 YYYYY

RECEIVE DOUBLE

BUFFER ENABLE

SUBADDRESS

CONTROL WORD

MSB

DATA BLOCK POINTER

LOOK-UP

TABLES

#1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BU-61582D2-491Q | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61582D2-491W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61582D2-491Y | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61582D2-501K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61582D2-590L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BU-61585 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |ACE |

| BU-61586 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |ACE |

| BU61586V6-300 | 制造商:DDC 功能描述:MIL-STD-1553/ARINC BUS CONTROLLER/RTU, 70 Pin, Flat Pack |

| BU-61588 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MINIATURE ADVANCED COMMUNICATION ENGINE (MINI-ACE) AND MINI-ACE PLUS |

| BU-61588F0 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MINIATURE ADVANCED COMMUNICATION ENGINE (MINI-ACE) AND MINI-ACE PLUS |

發(fā)布緊急采購,3分鐘左右您將得到回復。