- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4104 > ATF22LV10CQZ-30PU (Atmel)IC PLD 30NS 3.3V"QZ"POWER 24DIP PDF資料下載

參數(shù)資料

| 型號(hào): | ATF22LV10CQZ-30PU |

| 廠商: | Atmel |

| 文件頁(yè)數(shù): | 16/19頁(yè) |

| 文件大小: | 0K |

| 描述: | IC PLD 30NS 3.3V"QZ"POWER 24DIP |

| 標(biāo)準(zhǔn)包裝: | 15 |

| 系列: | 22V10 |

| 可編程類型: | EE PLD |

| 宏單元數(shù): | 10 |

| 輸入電壓: | 3.3V |

| 速度: | 30ns |

| 安裝類型: | 通孔 |

| 封裝/外殼: | 24-DIP(0.300",7.62mm) |

| 供應(yīng)商設(shè)備封裝: | 24-PDIP |

| 包裝: | 管件 |

| 產(chǎn)品目錄頁(yè)面: | 610 (CN2011-ZH PDF) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)

6

0779M–PLD–7/10

Atmel ATF22LV10C(Q)Z

4.4

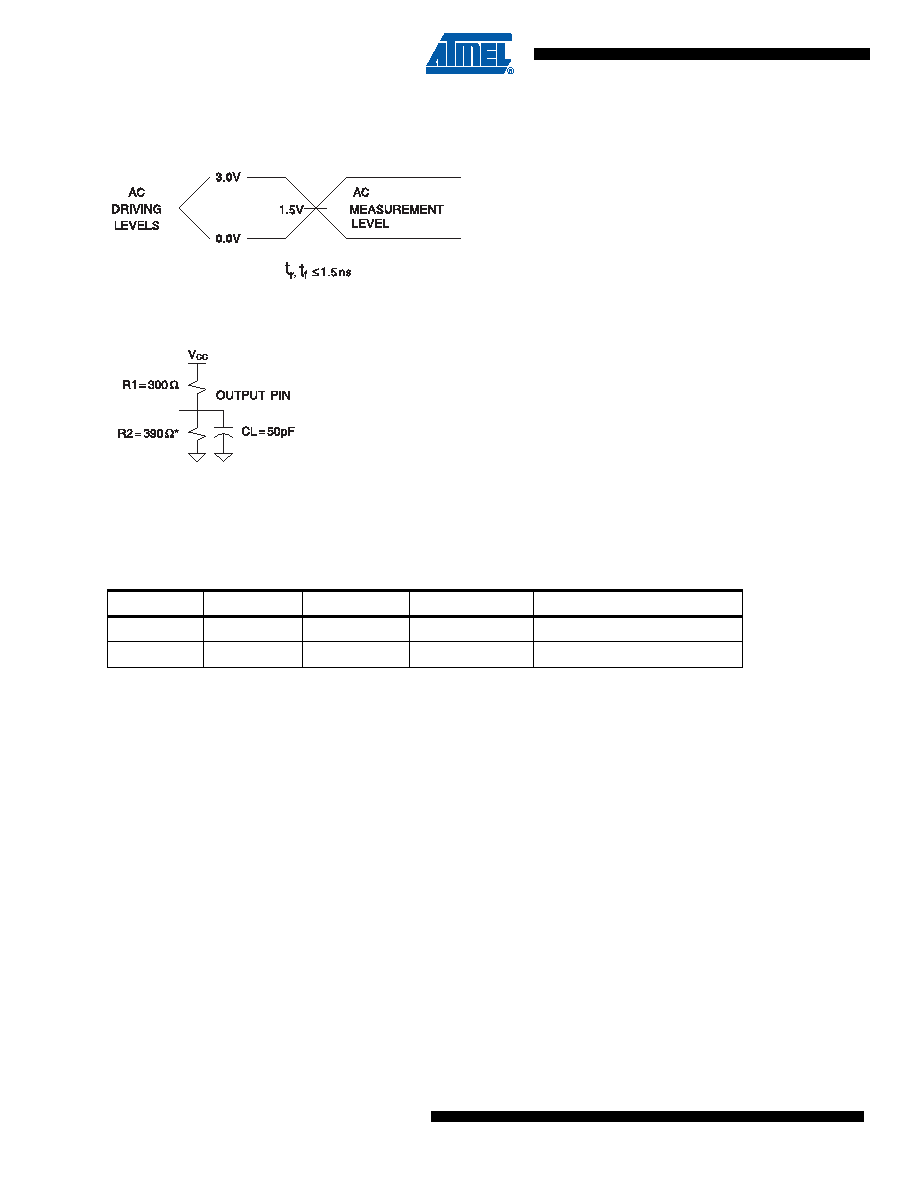

Input Test Waveforms

4.4.1

Input Test Waveforms and Measurement Levels

4.4.2

Output Test Loads

Note:

Similar competitors devices are specified with slightly different loads. These load differences may affect output signals’

delay and slew rate. Atmel devices are tested with sufficient margins to meet compatible device specification

conditions

4.5

Pin Capacitance

Table 4-1.

Pin Capacitance (f = 1MHz,T=25

C(1))

Note:

1. Typical values for nominal supply voltage. This parameter is only sampled and is not 100% tested

4.6

Power-up Reset

The registers in the Atmel ATF22LV10CZ/CQZ are designed to reset during power-up. At a point delayed slightly

from V

CC crossing VRST, all registers will be reset to the low state. The output state will depend on the polarity of the

buffer.

This feature is critical for state machine initialization. However, due to the asynchronous nature of reset and the

uncertainty of how V

CC actually rises in the system, the following conditions are required:

1.

The V

CC rise must be monotonic and start below 0.7V

2.

The clock must remain stable during T

PR

3.

After T

PR, all input and feedback setup times must be met before driving the clock pin high

4.7

Preload of Register Outputs

The ATF22LV10CZ/CQZ’s registers are provided with circuitry to allow loading of each register with either a high or

a low. This feature will simplify testing since any state can be forced into the registers to control test sequencing. A

JEDEC file with preload is generated when a source file with vectors is compiled. Once downloaded, the JEDEC

file preload sequence will be done automatically by most of the approved programmers after the programming.

Typ

Max

Units

Conditions

C

IN

5

8

pF

V

IN =0V

C

I/O

6

8

pF

V

OUT =0V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ATF22V10CQZ-20XU | IC PLD 20NS POWER 24TSSOP |

| AMM36DTBI | CONN EDGECARD 72POS R/A .156 SLD |

| ASM43DRMD | CONN EDGECARD 86POS .156 WW |

| FMC22DREI | CONN EDGECARD 44POS .100 EYELET |

| AMM12DREI | CONN EDGECARD 24POS .156 EYELET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ATF22LV10CQZ-30SC | 功能描述:SPLD - 簡(jiǎn)單可編程邏輯器件 500 GT 3.3-5V SPLY ZERO/QRTR PWR-30NS RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

| ATF22LV10CQZ-30SI | 功能描述:SPLD - 簡(jiǎn)單可編程邏輯器件 EEPLD 500 GATE 3.3 5V PWR 30NS IND TEMP RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

| ATF22LV10CQZ-30SU | 功能描述:SPLD - 簡(jiǎn)單可編程邏輯器件 500 GT 3.3-5V SPLY ZERO/QRTR PWR-30NS RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

| ATF22LV10CQZ-30XC | 功能描述:SPLD - 簡(jiǎn)單可編程邏輯器件 500 GT 3.3-5V SPLY ZERO/QRTR PWR-30NS RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

| ATF22LV10CQZ-30XI | 功能描述:SPLD - 簡(jiǎn)單可編程邏輯器件 500 GT 3.3-5V SPLY ZERO/QRTR PWR-30NS RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。