- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄166373 > ASI-L67201L-60 (ATMEL WIRELESS MICROCONTROLLERS) 512 X 9 OTHER FIFO, 60 ns, PQCC32 PDF資料下載

參數(shù)資料

| 型號: | ASI-L67201L-60 |

| 廠商: | ATMEL WIRELESS MICROCONTROLLERS |

| 元件分類: | FIFO |

| 英文描述: | 512 X 9 OTHER FIFO, 60 ns, PQCC32 |

| 封裝: | PLASTIC, LCC-32 |

| 文件頁數(shù): | 13/16頁 |

| 文件大小: | 146K |

| 代理商: | ASI-L67201L-60 |

L 67201/L 67202

MATRA MHS

Rev. C (10/11/95)

6

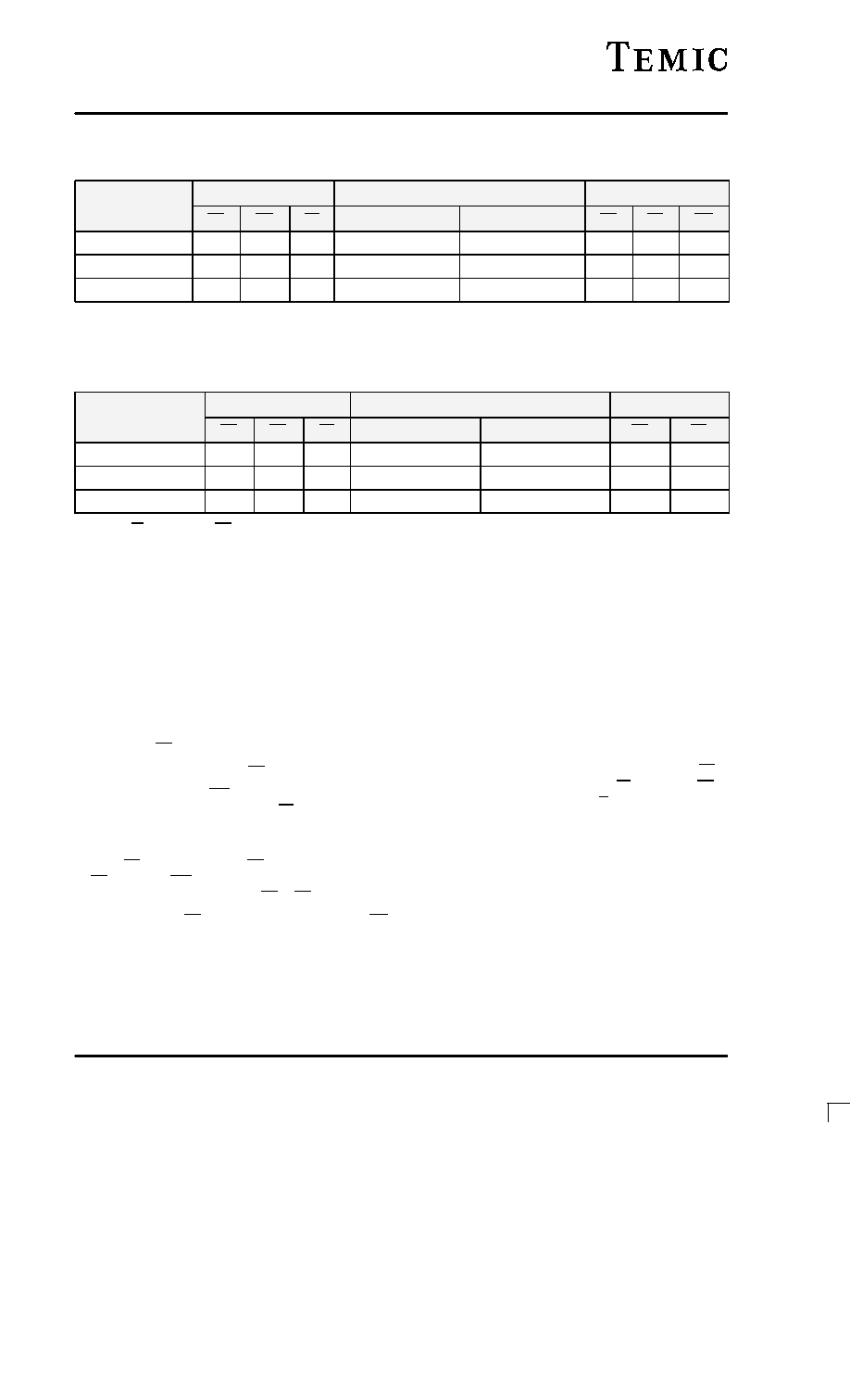

Table 1 : Reset and retransmit

Single Device Configuration/Width Expansion Mode

MODE

INPUTS

INTERNAL STATUS

OUTPUTS

MODE

RS

RT

XI

Read Pointer

Write Pointer

EF

FF

HF

Reset

0

X

0

Location Zero

0

1

Retransmit

1

0

Location Zero

Unchanged

X

Read/Write

1

0

Increment(4)

X

Note :

4. Pointer will increment if flag is high.

Table 2 : Reset and First Load Truth Table

Depth Expansion/Compound Expansion Mode

MODE

INPUTS

INTERNAL STATUS

OUTPUTS

MODE

RS

FL

XI

Read Pointer

Write Pointer

EF

FF

Reset First Device

0

(5)

Location Zero

0

1

Reset All Other Devices

0

1

(5)

Location Zero

0

1

Read/Write

1

X

(5)

X

Note :

5. XI is connected to XO of previous device.

See fig. 5.

Depth Expansion (Daisy Chain) Mode

The L 67201/202 can be easily adapted for applications

which require more than 512/1024 words. Figure 4

demonstrates Depth Expansion using three L 67201/202.

Any depth can be achieved by adding additional

67201/202.

The L 67201/202 operate in the Depth Expansion

configuration if the following conditions are met :

1. The first device must be designated by connecting the

First Load (FL) control input to ground.

2. All other devices must have FL in the high state.

3. The Expansion Out (XO) pin of each device must be

connected to the Expansion In (XI) pin of the next

device. See figure 4.

4. External logic is needed to generate a composite Full

Flag (FF) and Empty Flag (EF). This requires that all

EF’s and all FFs be Red (i.e. all must be set to

generate the correct composite FF or EF). See figure 4.

5. The Retransmit (RT) function and Half-Full Flag (HF)

are not available in the Depth Expansion Mode.

Compound Expansion Module

It is quite simple to apply the two expansion techniques

described above together to create large FIFO arrays (see

figure 5).

Bidirectional Mode

Applications which require data buffering between two

systems (each system being capable of Read and Write

operations) can be created by coupling L 67201/202 as

shown in figure 6. Care must be taken to ensure that the

appropriate flag is monitored by each system (i.e. FF is

monitored on the device on which W is in use ; EF is

monitored on the device on which R is in use). Both Depth

Expansion and Width Expansion may be used in this

mode.

Data Flow - Through Modes

Two types of flow-through modes are permitted : a read

flow-through and a write flow-through mode. In the read

flow-through mode (figure 17) the FIFO stack allows a

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ATIR0721DS | POSITION, LINEAR SENSOR-DIFFUSE, 1-1mm, 3mA, RECTANGULAR, SURFACE MOUNT |

| ATIR0821DS | POSITION, LINEAR SENSOR-DIFFUSE, 1-1mm, 3mA, RECTANGULAR, THROUGH HOLE MOUNT |

| ATL80/25-256VM | FPGA, 15600 GATES |

| ATL80/25-256QM | FPGA, 15600 GATES |

| ATL80/25-256AM | FPGA, 15600 GATES |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ASILUFC51 | 制造商:Schneider Electric 功能描述:AS-I/2 COMMUNICATION MODULE 制造商:SCHNEIDER ELECTRIC 功能描述:COMMUNICATION MODULE - FOR TESYS U |

| ASI-MA40232-119 | 制造商:ASI 制造商全稱:ASI 功能描述:SILICON DETECTOR DIODE |

| ASIMM8006 | 制造商:ASI 制造商全稱:ASI 功能描述:NPN SILICON HIGH FREQUENCY TRANSISTOR |

| ASIMRAL1720-9 | 制造商:ASI 制造商全稱:ASI 功能描述:NPN SILICON RF POWER TRANSISTOR |

| ASIMRAL2023-6 | 制造商:ASI 制造商全稱:ASI 功能描述:NPN SILICON RF POWER TRANSISTOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。