- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379688 > AS91L1003U40L100IF (Electronic Theatre Controls, Inc.) The AS91L1006BU is a one to 6-port JTAG gateway PDF資料下載

參數(shù)資料

| 型號: | AS91L1003U40L100IF |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | The AS91L1006BU is a one to 6-port JTAG gateway |

| 中文描述: | 該AS91L1006BU是一個6口的JTAG網(wǎng)關(guān) |

| 文件頁數(shù): | 1/28頁 |

| 文件大?。?/td> | 415K |

| 代理商: | AS91L1003U40L100IF |

當(dāng)前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

AS91L1006BU

July 2004

Description

The AS91L1006BU is a one to 6-port

JTAG gateway. It partitions a single JTAG chain

into six separate chains. These separate chains

can be optionally configured to operate as a single

chain.

The AS91L1006BU device is used to

provide enhanced capabilities to the standard

IEEE1149.1. It enables the IEEE1149.1 interface

to be used in a true Multi-Drop environment without

any additional signals. This Multi-Drop capability

enables the standard IEEE1149.1 interface to be

used not just for stand alone PCB (Printed Circuit

Board) testing, but also for complete system

testing including all PCBs within a system back

plane environment.

The AS91L1006BU provides the capability

of partitioning the PCB, into multiple smaller

IEEE1149.1 scan chains totally under software

Key Features

Device Multi-Drop addressable via the IEEE

1149.1 protocol

Support for 6 local scan chains addressable via

the IEEE 1149.1 interface

Support for Pass-Through

Support for the IEEE 1149.1 USERCODE

instruction

Support for Status instruction enabling non-

intrusive monitoring of the system card

Local Scan Port (LSP) enable signal provides the

ability to use non IEEE 1149.1 compliant devices

that require JTAG enable signal

6-Port JTAG Gateway

control. Partitioning the IEEE1149.1 chains on the

PCB has several benefits which include easier

fault diagnostics capabilities as a fault on one of

the IEEE1149.1 Local Scan Ports (LSPs) does

not render the PCB untestable, faster flash

programming on the PCBs, and removal of

IEEE1149.1 signal loading issues.

All

of

the

protocols

addressing the AS91L1006BU device via the

Multi-Drop capability and the protocols for

configuring which of the six IEEE1149.1 LSPs on

the AS91L1006BU are to be used, is handled via

3

rd

party ATPG tools from vendors like Asset-

Intertech and JTAG Technologies. In a Multi-Drop

environment it is also possible to perform

interconnect tests between multiple PCBs within a

system thus extending the interconnect tests to

the back plane itself.

required

for

Provides the ability to initiate Self-Test on a

remote PCB via a standard IEEE 1149.1

command

Support for JTAG Technologies AutoWR

feature

Pinout and feature set compatible (complete

second source) with the Firecron JTS06BU

device

Available in a 100-pin LQFP or a 100-pin

FPBGA lead free package

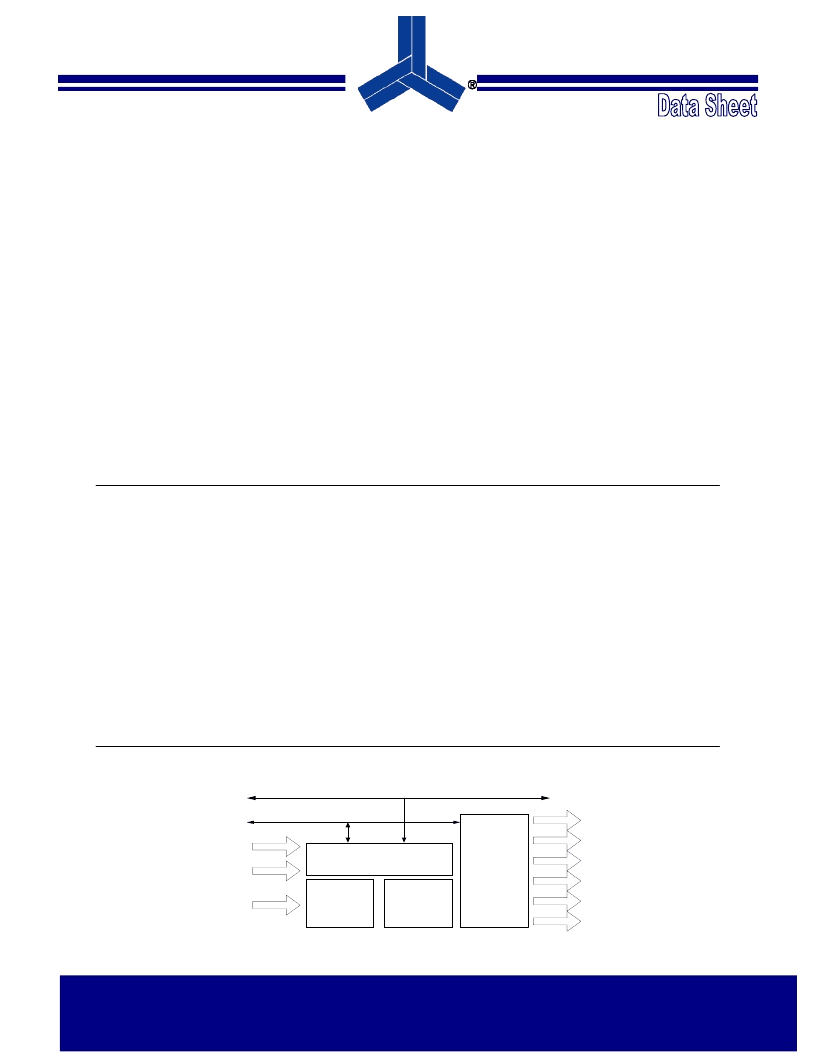

Device Block Diagram

SL o g ic

L P a rk/U n -p a rk

S yn c L o g ic

1 1 4 9 .1 T a n d

B o u n d a ry R e g iste r S e le ctio n L o g ic

L o g ic & L o ca l

CS C o n fig

lo g ic

L S P 1

L S P 2

L S P 3

L S P 4

L S P 5

L S P 6

S ta tu s D a ta

U se rco d e

D e vice

P a ss T h ro u g h E n a b le

P rim a ry 1 1 4 9 .1

Figure 1 - AS91L1006BU Device Block Diagram

Alliance Semiconductor

2575 Augustine Drive

Santa Clara, CA 95054

T: 408-855-4900

F: 408-855-4999

www.alsc.com

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AS91L1003U40L100IG | The AS91L1006BU is a one to 6-port JTAG gateway |

| AS91L1006S40F100C | The AS91L1006BU is a one to 6-port JTAG gateway |

| AS91L1006S40F100CF | The AS91L1006BU is a one to 6-port JTAG gateway |

| AS91L1006S40F100CG | The AS91L1006BU is a one to 6-port JTAG gateway |

| AS91L1006S40F100I | The AS91L1006BU is a one to 6-port JTAG gateway |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AS91L1003U40L100IG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:The AS91L1006BU is a one to 6-port JTAG gateway |

| AS91L1006BU | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:The AS91L1006BU is a one to 6-port JTAG gateway |

| AS91L1006BU10F100C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:The AS91L1006BU is a one to 6-port JTAG gateway |

| AS91L1006BU10F100CF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:The AS91L1006BU is a one to 6-port JTAG gateway |

| AS91L1006BU10F100CG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:The AS91L1006BU is a one to 6-port JTAG gateway |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。