- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366552 > AM85C30-8BQA (Advanced Micro Devices, Inc.) Enhanced Serial Communications Controller PDF資料下載

參數(shù)資料

| 型號: | AM85C30-8BQA |

| 廠商: | Advanced Micro Devices, Inc. |

| 英文描述: | Enhanced Serial Communications Controller |

| 中文描述: | 增強(qiáng)的串行通信控制器 |

| 文件頁數(shù): | 21/68頁 |

| 文件大小: | 553K |

| 代理商: | AM85C30-8BQA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

AMD

21

Am85C30

0

0

1

1

0

1

0

1

0

0

1

1

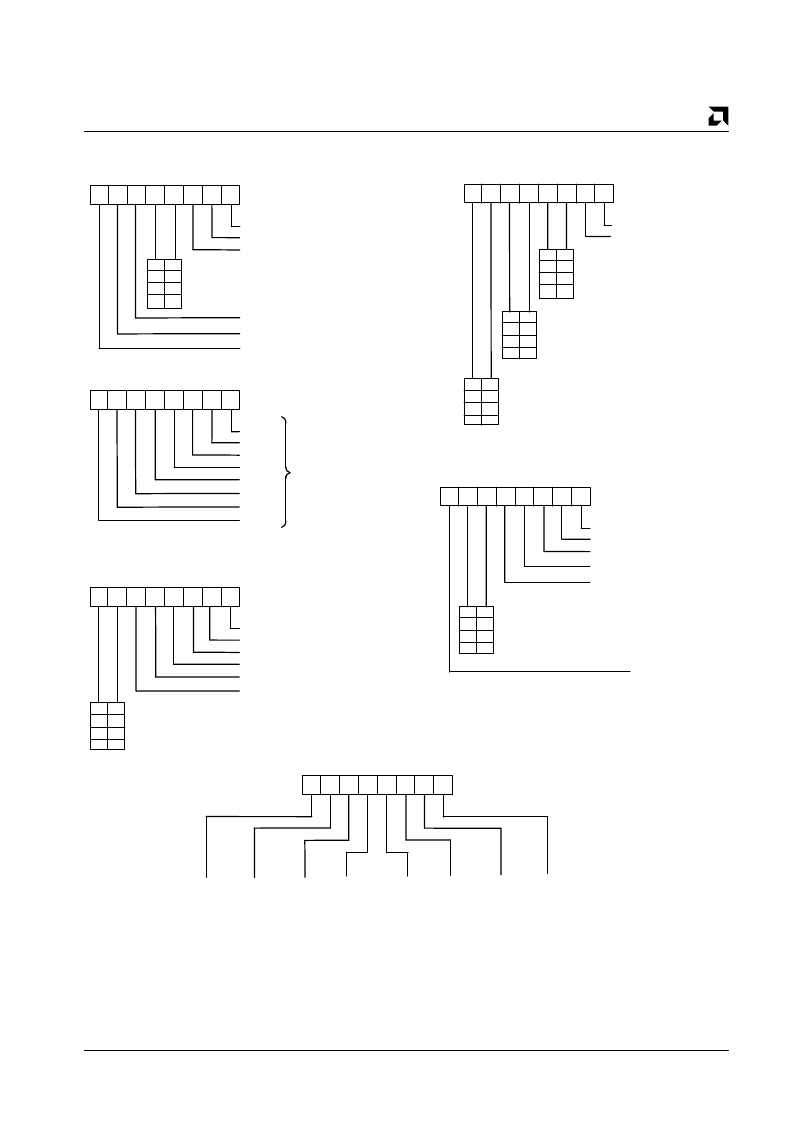

Write Register 1

Write Register 4

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

Ext Int Enable

Tx Int Enable

Parity is Special Condition

Rx Int Disable

Rx Int on First Character or Special Condition

Int on All Rx Characters or Special Condition

Rx Int on Special Condition only

Wait/DMA Request on Receive/Transmit

Wait/DMA Request Function

Wait/DMA Request Enable

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

Write Register 2

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

V0

V1

V2

V3

V4

V5

V6

V7

Interrupt Vector*

Write Register 6

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

0

1

0

1

0

0

1

1

0

1

0

1

0

0

1

1

0

1

0

1

Write Register 5

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

Tx CRC Enable

RTS

SDLC

/CRC-16

Tx Enable

Send Break

0

0

1

1

0

1

0

1

Write Register 3

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

Rx Enable

Sync Character Load Inhibit

Address Search Mode (SDLC)

Rx CRC Enable

Enter Hunt Mode

Auto Enable

0

0

1

1

0

1

0

1

Parity Enable

Parity Even/

Odd

Sync Modes Enable

1 Stop Bit/Character

1 1/2 Stop Bits/Character

2 Stop Bits/Character

8-Bit Sync Character

16-Bit Sync Character

SDLC Mode (01111110 Flag)

External Sync Mode

X1 Clock Mode

X16 Clock Mode

X32 Clock Mode

X64 Clock Mode

Tx 5 Bits (or less)/Character

Tx 7 Bits/Character

Tx 6 Bits/Character

Tx 8 Bits/Character

DTR

Rx 5 Bits/Character

Rx 7 Bits/Character

Rx 6 Bits/Character

Rx 8 Bits/Character

SYNC

7

SYNC

1

SYNC

7

SYNC

3

ADR

7

ADR

7

SYNC

6

SYNC

0

SYNC

6

SYNC

2

ADR

6

ADR

6

SYNC

5

SYNC

5

SYNC

5

SYNC

1

ADR

5

ADR

5

SYNC

4

SYNC

4

SYNC

4

SYNC

0

ADR

4

ADR

4

SYNC

3

SYNC

3

SYNC

3

1

ADR

3

1

SYNC

2

SYNC

2

SYNC

2

1

ADR

2

1

SYNC

1

SYNC

1

SYNC

1

1

ADR

1

1

SYNC

0

SYNC

0

SYNC

0

1

ADR

0

1

Monosync 8 Bits

Monosync 8 Bits

Bisync 16 Bits

Bisync 12 Bits

SDLC

SDLC (Address 0)

Figure 9. Write Register Bit Functions (continued)

10216F-13

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM8T-1203SC | 8 watt dc-dc converters |

| AM8T-1205DC | 8 watt dc-dc converters |

| AM8T-1205SC | 8 watt dc-dc converters |

| AM8T-1212DC | 8 watt dc-dc converters |

| AM8T-1212SC | 8 watt dc-dc converters |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM85C30-8BUA | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:Enhanced Serial Communications Controller |

| AM85C308JC | 制造商:AMD 功能描述:* |

| AM85C30-8JC | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:Enhanced Serial Communications Controller |

| AM85C308PC | 制造商:AMD 功能描述:_ |

| AM85C30-8PC | 制造商:AMD 功能描述:_ |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。