- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375289 > AM29BDS643GT5KVAI (SPANSION LLC) 64 Megabit (4 M x 16-Bit) CMOS 1.8 Volt-only Simultaneous Read/Write, Burst Mode Flash Memory PDF資料下載

參數(shù)資料

| 型號(hào): | AM29BDS643GT5KVAI |

| 廠商: | SPANSION LLC |

| 元件分類: | DRAM |

| 英文描述: | 64 Megabit (4 M x 16-Bit) CMOS 1.8 Volt-only Simultaneous Read/Write, Burst Mode Flash Memory |

| 中文描述: | 4M X 16 FLASH 1.8V PROM, 55 ns, PBGA44 |

| 封裝: | 9.20 X 8 MM, 0.50 MM PITCH, FBGA-44 |

| 文件頁數(shù): | 23/49頁 |

| 文件大小: | 382K |

| 代理商: | AM29BDS643GT5KVAI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當(dāng)前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁

May 8, 2006 25692A2

Am29BDS643G

21

D A T A S H E E T

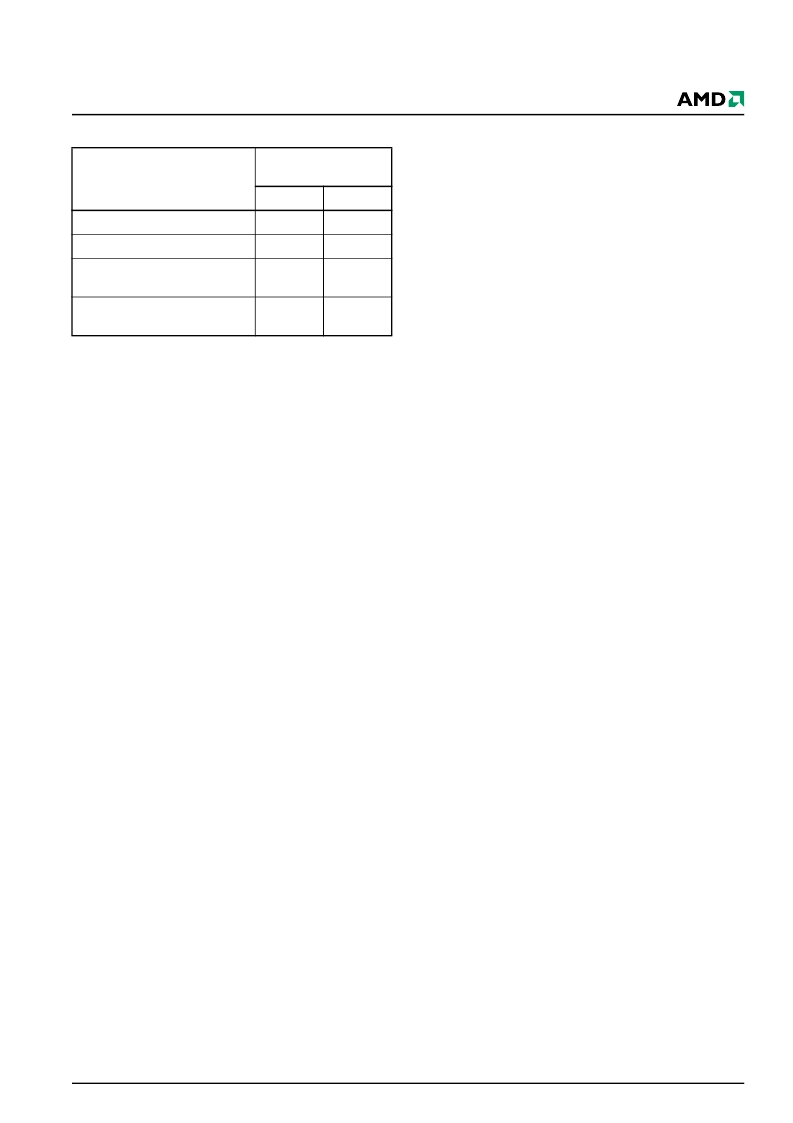

Table 9.

Wait States for Handshaking

* In the 8-, 16- and 32-word burst read modes, the address

pointer does not cross 64-word boundaries (addresses

which are multiples of 3Eh).

The autoselect function allows the host system to

determine whether the flash device is enabled for

handshaking. See the “Autoselect Command

Sequence” section for more information.

Enable PS (Power Saving) Mode

Command Sequence

The Enable PS (Power Saving) Mode command

sequence is required to set the device to the PS mode.

On power up, the Power Saving mode is disabled. The

command sequence consists of two unlock cycles fol-

lowed by a command cycle in which the address and

data should 555h/70h, respectively. The PS mode

remains enabled until the device is hardware reset

(either device is powered down or RESET# is asserted

low).

Sector Lock/Unlock Command Sequence

The sector lock/unlock command sequence allows the

system to determine which sectors are protected from

accidental writes. When the device is first powered up,

all sectors are locked. To unlock a sector, the system

must write the sector lock/unlock command sequence.

Two cycles are first written: addresses are don’t care

and data is 60h. During the third cycle, the sector

address (SLA) and unlock command (60h) is written,

while specifying with address A6 whether that sector

should be locked (A6 = V

IL

) or unlocked (A6 = V

IH

).

After the third cycle, the system can continue to lock or

unlock additional cycles, or exit the sequence by writing

F0h (reset command).

Note that the last two outermost boot sectors can be

locked by taking the WP# signal to V

IL

. Also, if V

PP

is at

V

IL

all sectors are locked; if the V

PP

input is at V

PP

, all

sectors are unlocked.

Reset Command

Writing the reset command resets the banks to the

read or erase-suspend-read mode. Address bits are

don’t cares for this command.

The reset command may be written between the

sequence cycles in an erase command sequence

before erasing begins. This resets the bank to which

the system was writing to the read mode. Once erasure

begins, however, the device ignores reset commands

until the operation is complete.

The reset command may be written between the

sequence cycles in a program command sequence

before programming begins. This resets the bank to

which the system was writing to the read mode. If the

program command sequence is written to a bank that

is in the Erase Suspend mode, writing the reset

command returns that bank to the erase-suspend-read

mode. Once programming begins, however, the device

ignores reset commands until the operation is com-

plete.

The reset command may be written between the

sequence cycles in an autoselect command sequence.

Once in the autoselect mode, the reset command must

be written to return to the read mode. If a bank entered

the autoselect mode while in the Erase Suspend mode,

writing the reset command returns that bank to the

erase-suspend-read mode.

If DQ5 goes high during a program or erase operation,

writing the reset command returns the banks to the

read mode (or erase-suspend-read mode if that bank

was in Erase Suspend).

Autoselect Command Sequence

The autoselect command sequence allows the host

system to access the manufacturer and device codes,

and determine whether or not a sector is protected.

Table 10 shows the address and data requirements.

The autoselect command sequence may be written to

an address within a bank that is either in the read or

erase-suspend-read mode. The autoselect command

may not be written while the device is actively program-

ming or erasing in the other bank.

The autoselect command sequence is initiated by first

writing two unlock cycles. This is followed by a third

write cycle that contains the bank address and the

autoselect command. The bank then enters the

autoselect mode. The system may read at any address

within the same bank any number of times without ini-

tiating another autoselect command sequence. The fol-

lowing table describes the address requirements for

the various autoselect functions, and the resulting data.

BA represents the bank address, and SA represents

Conditions at Address

Typical No. of Clock

Cycles after AVD# Low

40 MHz

54/66 MHz

Initial address is even

4

5

Initial address is odd

5

6

Initial address is even,

and is at boundary crossing*

6

7

Initial address is odd,

and is at boundary crossing*

7

8

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM29BDS643GT5MVAI | 64 Megabit (4 M x 16-Bit) CMOS 1.8 Volt-only Simultaneous Read/Write, Burst Mode Flash Memory |

| AM29BDS643GT7GVAI | 64 Megabit (4 M x 16-Bit) CMOS 1.8 Volt-only Simultaneous Read/Write, Burst Mode Flash Memory |

| AM29BDS643GT7KVAI | 64 Megabit (4 M x 16-Bit) CMOS 1.8 Volt-only Simultaneous Read/Write, Burst Mode Flash Memory |

| AM29BL162CB-120R | 16 Megabit (1 M x 16-Bit) CMOS 3.0 Volt-only Burst Mode Flash Memory |

| AM29BL162CB120RZE | 16 Megabit (1 M x 16-Bit) CMOS 3.0 Volt-only Burst Mode Flash Memory |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM29BL802CB-65RZET | 制造商:Spansion 功能描述: |

| AM29C01WW WAF | 制造商:Advanced Micro Devices 功能描述: |

| AM29C10API | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AM29C10AWW DIE | 制造商:Advanced Micro Devices 功能描述: |

| AM29C116-1JC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。