- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄201253 > ALVD-800MHZ-E-V-N100-T (ABRACON CORP) VCXO, CLOCK, 800 MHz, LVDS OUTPUT PDF資料下載

參數(shù)資料

| 型號: | ALVD-800MHZ-E-V-N100-T |

| 廠商: | ABRACON CORP |

| 元件分類: | VCXO, clock |

| 英文描述: | VCXO, CLOCK, 800 MHz, LVDS OUTPUT |

| 封裝: | ROHS COMPLIANT, CERAMIC, SMD, 6 PIN |

| 文件頁數(shù): | 1/3頁 |

| 文件大小: | 1702K |

| 代理商: | ALVD-800MHZ-E-V-N100-T |

ALVD

| | | | | | | | | | | | | | |

WITH VOLTAGE CONTROL

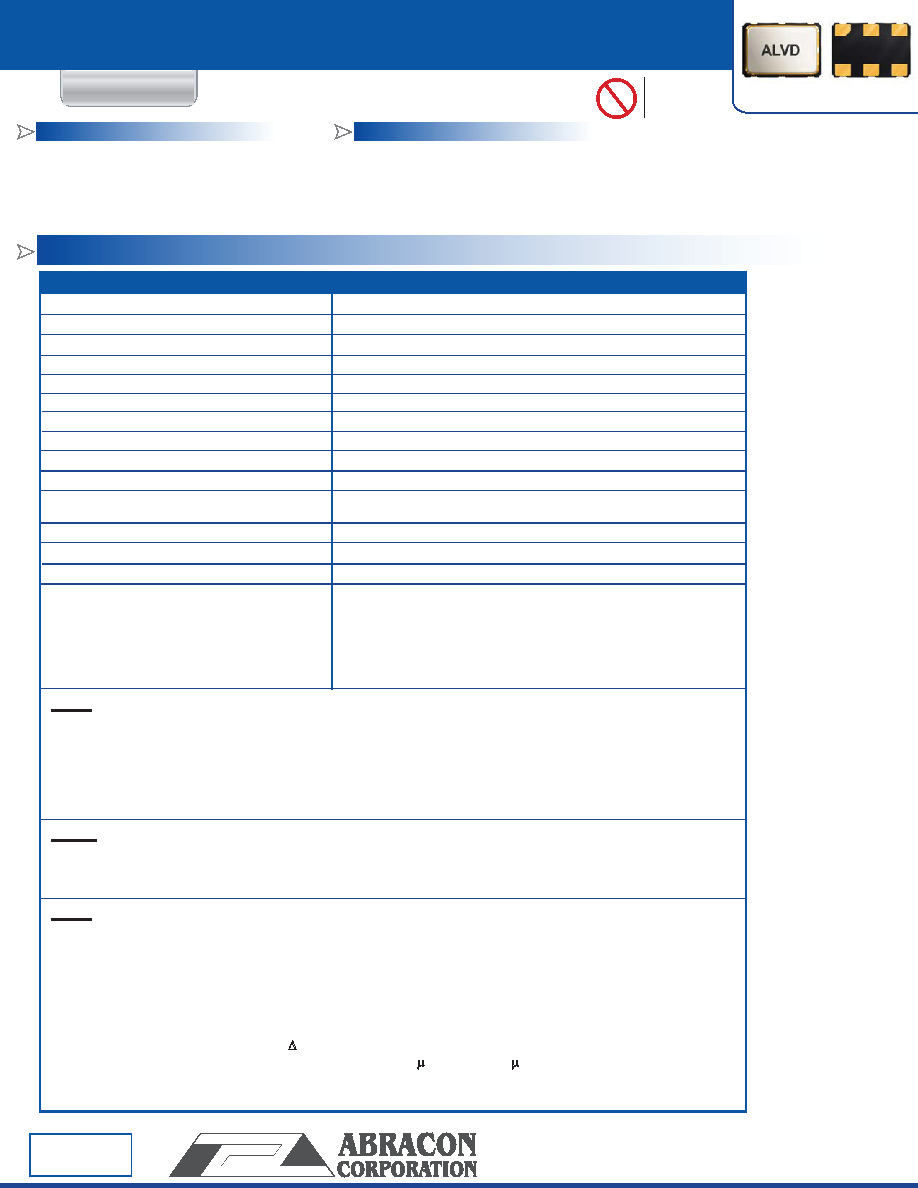

STANDARD SPECIFICATIONS:

APPLICATIONS:

SONET, xDSL

SDH, CPE

STB

FEATURES:

Based on a proprietary digital multiplier

Tri-State Output

Low Phase Jitter

3.3V +/- 5% operation

Ceramic SMD, low profile package

7.0 x 5.0 x 1.8mm

Pb RoHS

Compliant

ABRACON IS

ISO 9001 / QS 9000

CERTIFIED

ABRACON IS

ISO 9001 / QS 9000

CERTIFIED

CERAMIC SMD CRYSTAL CLOCK OSCILLATOR

30332 Esperanza, Rancho Santa Margarita, California 92688

tel 949-546-8000 | fax 949-546-8001 | www.abracon.com

Revised: 07.22.09

Visit www.abracon.com for Terms & Conditions of Sale

P

ABRACON P/N:

ALVD Series

Frequency range:

750 KHz to 800 MHz

Operating temperature:

0°C to +70°C (see options)

Storage temperature:

-55°C to +125°C

Overall frequency stability:

±50 ppm max. (see options)

Supply voltage (Vdd):

3.3V ± 10%

Voltage control (VC):

0.3VDC min, 1.65VDC typ, 3.0 VDC max.

Symmetry at 1/2 Vdd:

40/60% max.

Output Level:

See options (PECL, CMOS, or LVDS)

Pullability:

± 50ppm (see option)

Tristate Function:

"1" (VIH >= 0.7* Vdd) or open: Oscillation

"0" (VIL < 0.3* Vdd) : Hi Z

Aging per year:

±5 ppm max.

RMS Phase Jitter:

3ps typical, 5ps max. (12KHz~20MHz)

Period Jitter (peak to peak):

35 ps typical

Phase Noise:

-112 dBc/Hz @ 1kHz Offset from 155.52MHz

-125 dBc/Hz @ 10kHz Offset from 155.52MHz

-123 dBc/Hz @ 100KHz Offset from 155.52MHz

-109 dBc/Hz @ 1kHz Offset from 622.08MHz

-110 dBc/Hz @ 10kHz Offset from 622.08MHz

-109 dBc/Hz @ 100KHz Offset from 622.08MHz

PECL:

Supply current (IDD):25mA max (for Fo<24MHz),65mA max (for 24MHz<Fo<96MHz),100mA max (96MHz<Fo<700MHz)

Output Logic High:

Vdd-1.025V min, Vdd-0.880V max.

Output Logic Low:

Vdd-1.810V min. Vdd-1.620V max.

Symmetry (Duty Cycle):

45% min, 50% typ, 55% max,

Rise time:

0.6nSec typ,1.5nS max

Fall time:

0.6nSec typ, 1.5nS max

CMOS:

Supply current (IDD):15mA max (for Fo<24MHz),30mA max (for 24MHz<Fo<96MHz), 40mA max (96MHz<Fo<700MHz)

Output Clock Rise/ Fall Time [10%~90% VDD with 10pF load]:

1.2ns typ, 1.6ns max.

Output Clock Duty Cycle [Measured @ 50% VDD]:

45% min, 50% typical, 55% max

LVDS:

Supply current (IDD):25mA max (for Fo<24MHz),45mA max (for 24MHz<Fo<96MHz),80mA max (96MHz<Fo<700MHz)

Output Clock Duty Cycle @ 1.25V:

45% min, 50% typical, 55% max

Output Differential Voltage (VOD): 247mV min, 355mV typical, 454mV max

VDD Magnitude Change (? VOD): -50mV min, 50mV max

Output High Voltage :

VOH = 1.4V typical, 1.6V max.

Output Low Voltage:

VOL = 0.9V min, 1.1V typical

Offset Voltage [RL = 100?? : VOS = 1.125V min, 1.2V typical, 1.375V max

Offset Magnitude Change [RL = 100?? : ? VOS = 0mV min, 3mV typical, 25mV max

Power-off Leakage (IOXD) [Vout=VDD or GND, VDD=0V] = ±1? A typical, ±10? A max.

Differential Clock Rise Time (tr) [RL=100? , CL=10pF]: 0.2nS min, 0.7nS typical, 1.0nS,max

Differential Clock Fall Time (tf) [RL=100? , CL=10pF]: 0.2nS min, 0.7nS typical, 1.0nS max

ARAMETERS

相關PDF資料 |

PDF描述 |

|---|---|

| ASEV4-27MHZ-F-K-T | VCXO, CLOCK, 27 MHz, CMOS OUTPUT |

| ASEV4-27MHZ-I-B-T | VCXO, CLOCK, 27 MHz, CMOS OUTPUT |

| ALVD-0.750MHZ-H-C-N100 | VCXO, CLOCK, 0.75 MHz, CMOS OUTPUT |

| ASEV4-27MHZ-N-T | VCXO, CLOCK, 27 MHz, CMOS OUTPUT |

| ASEV4-32.768MHZ-D-J-T | VCXO, CLOCK, 32.768 MHz, CMOS OUTPUT |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AL-VLS | 制造商:Mitsubishi Electric 功能描述:SOFTWARE ALPHA LOGIC |

| ALVLSV2.32 | 制造商:Mitsubishi Electric 功能描述:Alpha 2 PLC programming software |

| ALVN31611N-R | 制造商:IDEC CORPORATION 功能描述:Illuminated E-Stop Red 30mm |

| ALVR031K000FE12 | 功能描述:RES 1K OHM 1% WW AXIAL RoHS:是 類別:電阻器 >> 通孔電阻器 系列:ALVR 產(chǎn)品培訓模塊:Power Resistor Heatsinks 標準包裝:60 系列:PF1260 電阻(歐姆):4.7 功率(瓦特):20W 復合體:薄膜 特點:- 溫度系數(shù):±100ppm/°C 容差:±1% 封裝/外殼:TO-126-2 尺寸/尺寸:0.335" L x 0.122" W(8.50mm x 3.10mm) 高度:0.591"(15.00mm) 端子數(shù):2 包裝:管件 |

| ALVR0347R00FE12 | 功能描述:RES 47 OHM 1% WW AXIAL RoHS:是 類別:電阻器 >> 通孔電阻器 系列:ALVR 產(chǎn)品培訓模塊:Current Sensing Resistors 標準包裝:50 系列:TK 電阻(歐姆):10 功率(瓦特):20W 復合體:厚膜 特點:電流檢測 溫度系數(shù):±200ppm/°C 容差:±5% 封裝/外殼:TO-220-2 尺寸/尺寸:0.394" L x 0.177" W(10.00mm x 4.50mm) 高度:0.701"(17.80mm) 端子數(shù):2 包裝:管件 相關產(chǎn)品:6200-ND - MOUNTING BRACKET KIT FOR TK/TN |

發(fā)布緊急采購,3分鐘左右您將得到回復。