- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374048 > ADV7391BCPZ-REEL (ANALOG DEVICES INC) Low Power, Chip Scale 10-Bit SD/HD Video Encoder PDF資料下載

參數(shù)資料

| 型號(hào): | ADV7391BCPZ-REEL |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 顏色信號(hào)轉(zhuǎn)換 |

| 英文描述: | Low Power, Chip Scale 10-Bit SD/HD Video Encoder |

| 中文描述: | COLOR SIGNAL ENCODER, QCC32 |

| 封裝: | 5 X 5 MM, ROHS COMPLIANT, MO-220VHHD-2, LFSCP-32 |

| 文件頁(yè)數(shù): | 91/96頁(yè) |

| 文件大小: | 1209K |

| 代理商: | ADV7391BCPZ-REEL |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)當(dāng)前第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)

ADV7390/ADV7391/ADV7392/ADV7393

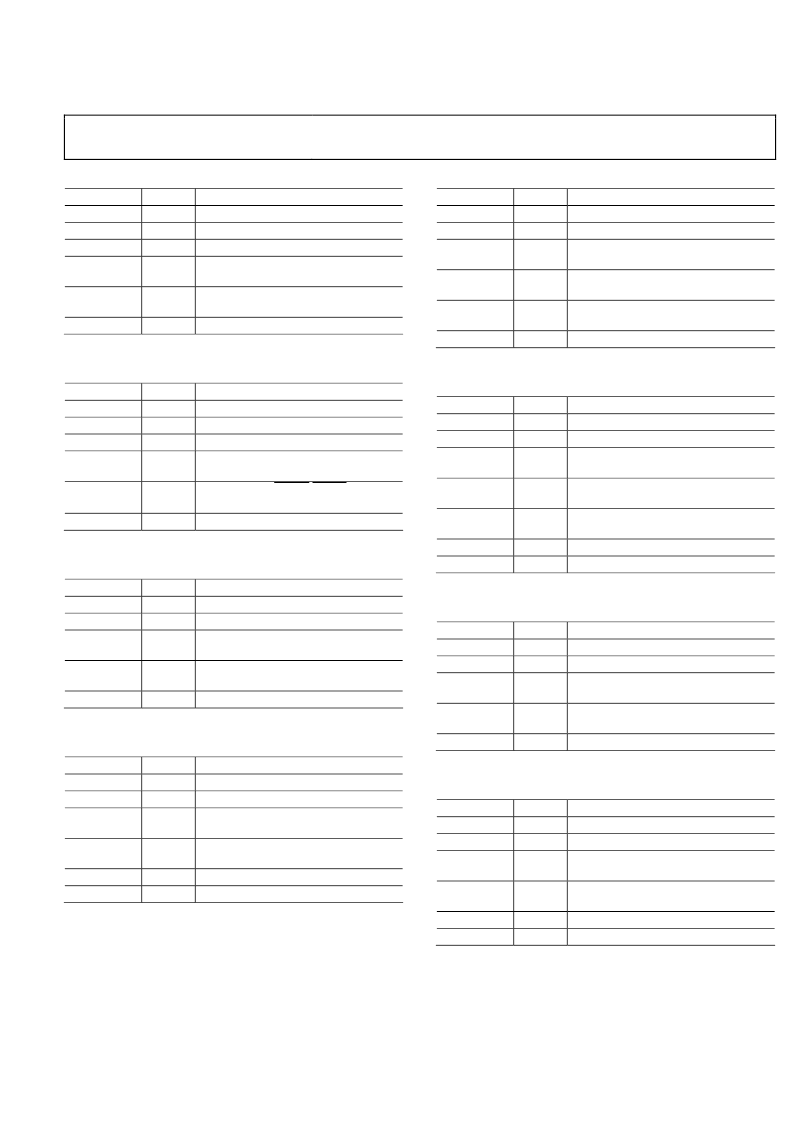

Table 96. 16-Bit 625p YCrCb In (EAV/SAV), RGB Out

Subaddress

Setting Description

0x17

0x02

Software reset.

0x00

0x1C

All DACs enabled. PLL enabled (8×).

0x01

0x10

ED-SDR input mode.

0x02

0x10

RGB output enabled. RGB output sync

enabled.

0x30

0x1C

625p @ 50 Hz. EAV/SAV synchroniza-

tion. EIA-770.2 output levels.

0x31

0x01

Pixel data valid.

Rev. 0 | Page 91 of 96

Table 97. 16-Bit 625p YCrCb In, RGB Out

Subaddress

Setting Description

0x17

0x02

0x00

0x1C

0x01

0x10

0x02

0x10

Software reset.

All DACs enabled. PLL enabled (8×).

ED-SDR input mode.

RGB output enabled. RGB output sync

enabled.

625p @ 50 Hz. HSYNC/VSYNC synch-

ronization. EIA-770.2 output levels.

Pixel data valid.

0x30

0x18

0x31

0x01

Table 98. 8-Bit 525p YCrCb In (EAV/SAV), YPrPb Out

Subaddress

Setting Description

0x17

0x02

Software reset.

0x00

0x1C

All DACs enabled. PLL enabled (8×).

0x01

0x20

ED-DDR input mode. Luma data

clocked on falling edge of CLKIN.

0x30

0x04

525p @ 59.94 Hz. EAV/SAV synchro-

nization. EIA-770.2 output levels.

0x31

0x01

Pixel data valid.

Table 99. 10-Bit 525p YCrCb In (EAV/SAV), YPrPb Out

Subaddress

Setting Description

0x17

0x02

Software reset.

0x00

0x1C

All DACs enabled. PLL enabled (8×).

0x01

0x20

ED-DDR input mode. Luma data

clocked on falling edge of CLKIN.

0x30

0x04

525p @ 59.94 Hz. EAV/SAV synchro-

nization. EIA-770.2 output levels.

0x31

0x01

Pixel data valid.

0x33

0x6C

10-bit input enabled.

Table 100. 8-Bit 525p YCrCb In (EAV/SAV), RGB Out

Subaddress

Setting

Description

0x17

0x02

Software reset.

0x00

0x1C

All DACs enabled. PLL enabled (8×).

0x01

0x20

ED-DDR input mode. Luma data

clocked on falling edge of CLKIN.

0x02

0x10

RGB output enabled. RGB output sync

enabled.

0x30

0x04

525p @ 59.94 Hz. EAV/SAV synchro-

nization. EIA-770.2 output levels.

0x31

0x01

Pixel data valid.

Table 101. 10-Bit 525p YCrCb In (EAV/SAV), RGB Out

Subaddress

Setting

Description

0x17

0x02

Software reset.

0x00

0x1C

All DACs enabled. PLL enabled (8×).

0x01

0x20

ED-DDR input mode. Luma data

clocked on falling edge of CLKIN.

0x02

0x10

RGB output enabled. RGB output sync

enabled.

0x30

0x04

525p @ 59.94 Hz. EAV/SAV synchro-

nization. EIA-770.2 output levels.

0x31

0x01

Pixel data valid.

0x33

0x6C

10-bit input enabled.

Table 102. 8-Bit 625p YCrCb In (EAV/SAV), YPrPb Out

Subaddress

Setting

Description

0x17

0x02

Software reset.

0x00

0x1C

All DACs enabled. PLL enabled (8×).

0x01

0x20

ED-DDR input mode. Luma data

clocked on falling edge of CLKIN.

0x30

0x1C

625p @ 50 Hz. EAV/SAV synchroniza-

tion. EIA-770.2 output levels.

0x31

0x01

Pixel data valid.

Table 103. 10-Bit 625p YCrCb In (EAV/SAV), YPrPb Out

Subaddress

Setting

Description

0x17

0x02

Software reset.

0x00

0x1C

All DACs enabled. PLL enabled (8×).

0x01

0x20

ED-DDR input mode. Luma data

clocked on falling edge of CLKIN.

0x30

0x1C

625p @ 50 Hz. EAV/SAV synchroniza-

tion. EIA-770.2 output levels.

0x31

0x01

Pixel data valid.

0x33

0x6C

10-bit input enabled.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADV7391EBZ | Low Power, Chip Scale 10-Bit SD/HD Video Encoder |

| ADV7392 | Low Power, Chip Scale 10-Bit SD/HD Video Encoder |

| ADV7392BCPZ | Low Power, Chip Scale 10-Bit SD/HD Video Encoder |

| ADV7392BCPZ-REEL | Low Power, Chip Scale 10-Bit SD/HD Video Encoder |

| ADV7392EBZ | Low Power, Chip Scale 10-Bit SD/HD Video Encoder |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADV7391EBZ | 制造商:AD 制造商全稱:Analog Devices 功能描述:Low Power, Chip Scale 10-Bit SD/HD Video Encoder |

| ADV7391WBCPZ | 制造商:Analog Devices 功能描述: |

| ADV7391WBCPZ-RL | 制造商:Analog Devices 功能描述: |

| ADV7392 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Low Power, Chip Scale 10-Bit SD/HD Video Encoder |

| ADV7392BCPZ | 制造商:Analog Devices 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。