- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374045 > ADV7120KN50 (ANALOG DEVICES INC) CAP 0.022UF 50V 2% NP0(C0G) AXIAL RAD.40 BULK S-MIL-PRF-20 PDF資料下載

參數(shù)資料

| 型號: | ADV7120KN50 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | DAC |

| 英文描述: | CAP 0.022UF 50V 2% NP0(C0G) AXIAL RAD.40 BULK S-MIL-PRF-20 |

| 中文描述: | TRIPLE, PARALLEL, 8 BITS INPUT LOADING, 8-BIT DAC, PDIP40 |

| 封裝: | 0.6 INCH, PLASTIC, DIP-40 |

| 文件頁數(shù): | 9/12頁 |

| 文件大小: | 188K |

| 代理商: | ADV7120KN50 |

ADV7120

REV. B

–9–

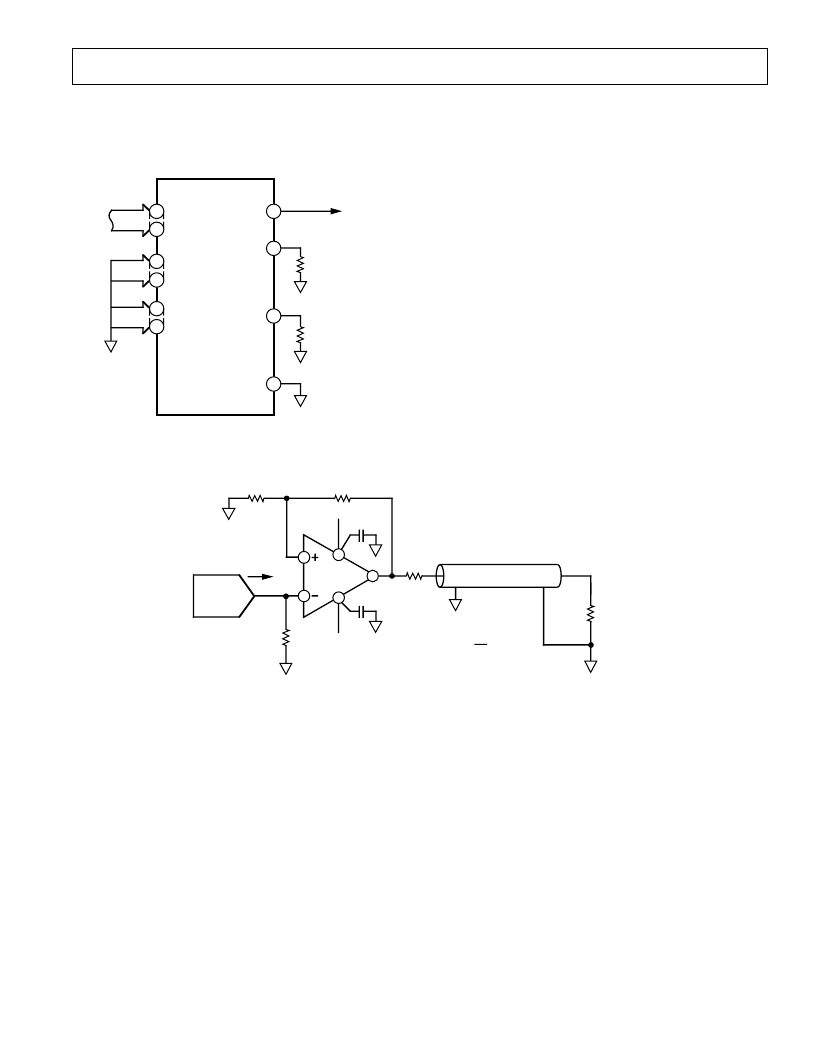

T he unused analog outputs should be terminated with the same

load as that for the used channel. In other words, if the red

channel is used and IOR is terminated with a doubly terminated

75

load (37.5

), IOB and IOG should be terminated with

37.5

resistors. (See Figure 6.)

GND

ADV7120

R0

R7

G0

G7

B0

B7

VIDEO

INPUT

DOUBLY

TERMINATED

75

LOAD

IOR

IOG

IOB

37.5

37.5

Figure 6. Input and Output Connections for Stand-Alone

Gray Scale or Composite Video

Video Output Buffers

T he ADV7120 is specified to drive transmission line loads,

which is what most monitors are rated as. T he analog output

configurations to drive such loads are described in the Analog

Interface section and illustrated in Figure 5. However, in some

applications it may be required to drive long “transmission line”

cable lengths. Cable lengths greater than 10 meters can attenu-

ate and distort high frequency analog output pulses. T he inclu-

sion of output buffers will compensate for some cable distortion.

Buffers with large full power bandwidths and gains between 2

and 4 will be required.

T hese buffers will also need to be able to supply sufficient cur-

rent over the complete output voltage swing. Analog Devices

produces a range of suitable op amps for such applications.

T hese include the AD84X series of monolithic op amps. In very

high frequency applications (80 MHz), the AD9617 is recom-

mended. More information on line driver buffering circuits is

given in the relevant op amp data sheets.

Use of buffer amplifiers also allows implementation of other

video standards besides RS-343A and RS-170. Altering the gain

components of the buffer circuit will result in any desired

video level.

7

6

4

3

2

AD848

DACs

IOR, IOG, IOB

(CABLE)

Z

O

= 75

Z

= 75

(SOURCE

TERMINATION)

Z

= 75

(MONITOR)

0.1

μ

F

75

+V

S

Z

1

Z

2

–V

S

0.1

μ

F

GAIN (G) = 1 +

Z

1

Z

2

Figure 7. AD848 As an Output Buffer

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADV7120KN80 | CAP 0.022UF 50V 5% NP0(C0G) AXIAL RAD.40 BULK R-MIL-PRF-20 |

| ADV7120KN30 | CAP 0.022UF 50V 2% NP0(C0G) AXIAL RAD.40 BULK R-MIL-PRF-20 |

| ADV7121KN50 | CMOS 80 MHz, Triple 10-Bit Video DACs |

| ADV7121KN80 | CMOS 80 MHz, Triple 10-Bit Video DACs |

| ADV7122KST30 | CMOS 80 MHz, Triple 10-Bit Video DACs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADV7120KN80 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ADV7120KP30 | 制造商:Analog Devices 功能描述:DAC 3-CH Segment 8-bit 44-Pin PLCC 制造商:Rochester Electronics LLC 功能描述:TRIPLE 8 BIT VIDEO DAC IC - Bulk 制造商:Analog Devices 功能描述:IC 8-BIT VIDEO DAC |

| ADV7120KP30-REEL | 制造商:Analog Devices 功能描述:DAC 3-CH Segment 8-bit 44-Pin PLCC T/R 制造商:Rochester Electronics LLC 功能描述:TRIPLE 8-BIT VIDEO DAC IC - Tape and Reel |

| ADV7120KP50 | 制造商:Analog Devices 功能描述:DAC 3-CH Segment 8-bit 44-Pin PLCC 制造商:Rochester Electronics LLC 功能描述:TRIPLE 8 BIT VIDEO DAC IC - Bulk |

| ADV7120KP50-REEL | 制造商:Analog Devices 功能描述:DAC 3-CH Segment 8-bit 44-Pin PLCC T/R 制造商:Rochester Electronics LLC 功能描述:TRIPLE 8 BIT VIDEO DAC IC - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。