- 您現在的位置:買賣IC網 > PDF目錄374035 > ADSP-2173BS-80 (ANALOG DEVICES INC) DSP Microcomputer PDF資料下載

參數資料

| 型號: | ADSP-2173BS-80 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數字信號處理 |

| 英文描述: | DSP Microcomputer |

| 中文描述: | 24-BIT, 10 MHz, OTHER DSP, PQFP128 |

| 封裝: | PLASTIC, QFP-128 |

| 文件頁數: | 35/52頁 |

| 文件大?。?/td> | 664K |

| 代理商: | ADSP-2173BS-80 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

ADSP-2171/ADSP-2172/ADSP-2173

REV. A

–35–

ADSP-2173

Parameter

Min

Max

Unit

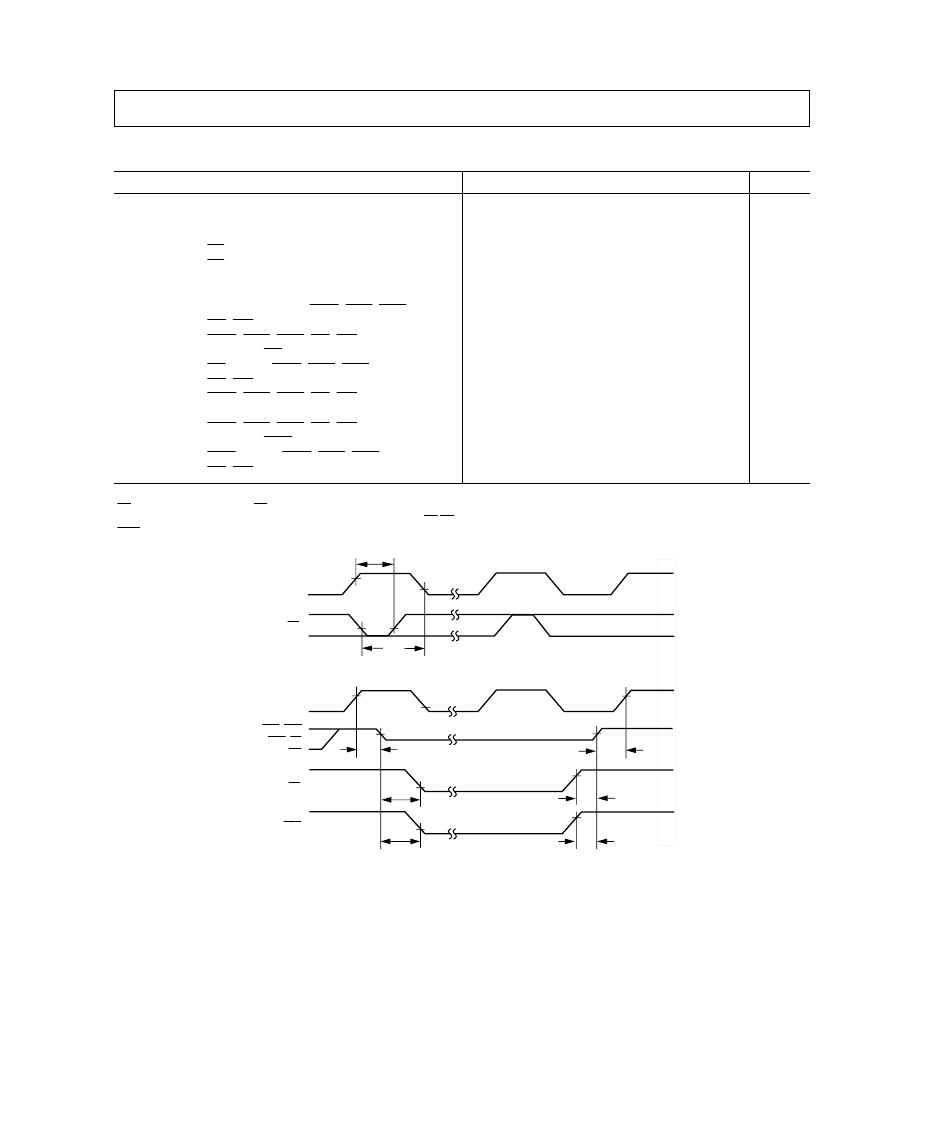

Bus Request/Grant

T iming Requirement:

t

BH

t

BS

BR

Hold after CLK OUT High

1

BR

Setup before CLK OUT Low

1

0.25t

CK

+ 2

0.25t

CK

+ 22

ns

ns

Switching Characteristic:

t

SD

CLK OUT High to

DMS

,

PMS

,

BMS

,

RD

,

WR

Disable

DMS

,

PMS

,

BMS

,

RD

,

WR

Disable to

BG

Low

BG

High to

DMS

,

PMS

,

BMS

,

RD

,

WR

Enable

DMS

,

PMS

,

BMS

,

RD

,

WR

Enable to CLK OUT High

DMS

,

PMS

,

BMS

,

RD

,

WR

Disable to

BGH

Low

2

BGH

High to

DMS

,

PMS

,

BMS

,

RD

,

WR

Enable

2

0.25t

CK

+ 16

ns

t

SDB

0

ns

t

SE

0

ns

t

SEC

0.25t

CK

– 10

ns

t

SDBH

0

ns

t

SEH

0

ns

NOT ES

1

BR

is an asynchronous signal. If

BR

meets the setup/hold requirements, it will be recognized during the current clock cycle; otherwise the signal will be recognized

on the following cycle. Refer to the

ADSP-2100 Family User’s Manual

for

BR

/

BG

cycle relationships.

2

BGH

is asserted when the bus is granted and the processor requires control of the bus to continue.

t

BS

BR

t

BH

CLKOUT

PMS

,

DMS

BMS

,

RD

WR

BG

CLKOUT

t

SD

t

SDB

t

SE

t

SEC

t

SDBH

BGH

t

SEH

Figure 26. Bus Request–Bus Grant

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-2171 | DSP Microcomputer(DSP 微計算機) |

| ADSP-2172 | DSP Microcomputer(DSP 微計算機) |

| ADSP-2173 | DSP Microcomputer(DSP 微計算機) |

| ADSP-2181BS-115 | DSP Microcomputer |

| ADSP-2181BS-133 | DSP Microcomputer |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADSP-2173BST-80 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 20MHz 20MIPS 128-Pin TQFP 制造商:Rochester Electronics LLC 功能描述:16BIT FXD PT PROC 3.3V - Bulk |

| ADSP-2176-760040 | 制造商:Analog Devices 功能描述: |

| ADSP-2176-760061 | 制造商:Analog Devices 功能描述: |

| ADSP-2176-760243 | 制造商:Analog Devices 功能描述: |

| ADSP-2178-780244 | 制造商:AD 制造商全稱:Analog Devices 功能描述:GSM Baseband Processing Chipset |

發(fā)布緊急采購,3分鐘左右您將得到回復。