- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373989 > ADG663 (Analog Devices, Inc.) Tantalum Molded Capacitor; Capacitance: 33uF; Voltage: 10V; Case Size: 3.4x1.9 mm; Packaging: Tape & Reel PDF資料下載

參數(shù)資料

| 型號: | ADG663 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Tantalum Molded Capacitor; Capacitance: 33uF; Voltage: 10V; Case Size: 3.4x1.9 mm; Packaging: Tape & Reel |

| 中文描述: | LC2MOS精密5伏四路SPST開關(guān) |

| 文件頁數(shù): | 8/8頁 |

| 文件大小: | 123K |

| 代理商: | ADG663 |

–8–

REV. 0

C

P

ADG661/ADG662/ADG663

S

D

0.1

m

F

V

DD

IN

V

S

GND

V

SS

R

L

50

V

V

OUT

0.1

m

F

V

IN

V

SS

V

DD

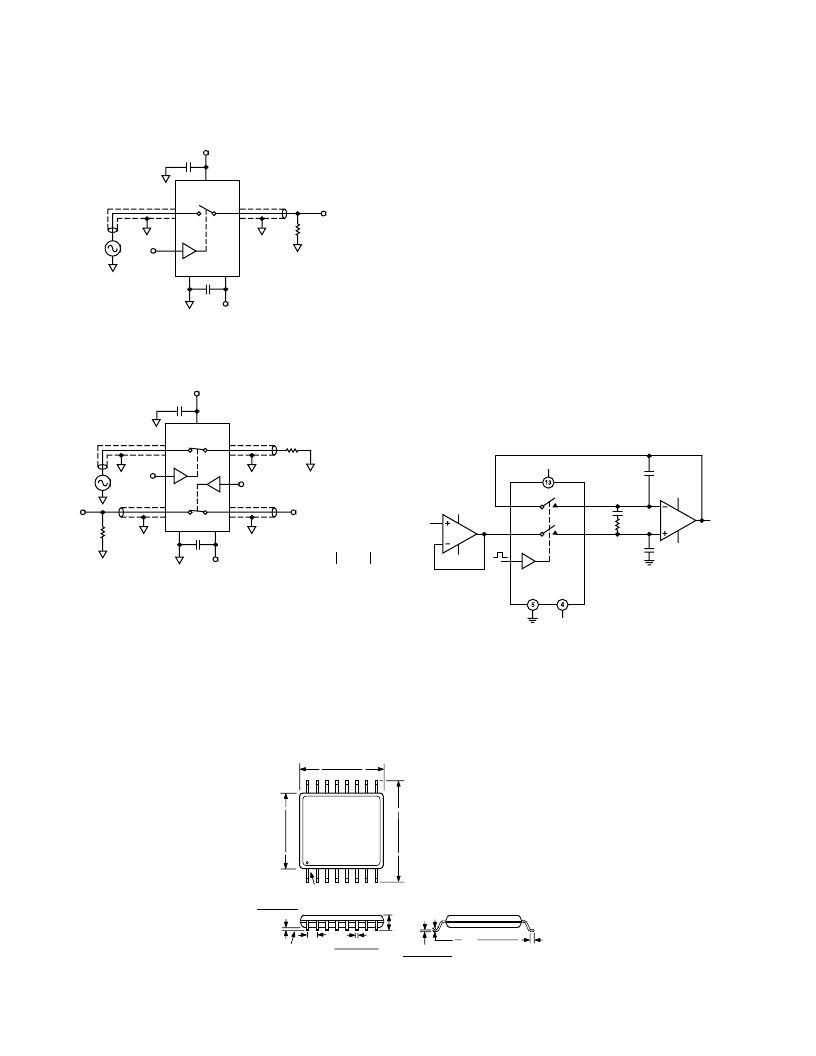

7. Off Isolation

16-Lead T SSOP

(RU-16)

16

9

8

1

0.201 (5.10)

0.193 (4.90)

0

0

0

0

PIN 1

SEATING

PLANE

0.006 (0.15)

0.002 (0.05)

0.0118 (0.30)

0.0075 (0.19)

0.0256

(0.65)

BSC

0.0433

(1.10)

MAX

0.0079 (0.20)

0.0035 (0.090)

0.028 (0.70)

0.020 (0.50)

8°

0°

OUT LINE DIME NSIONS

Dimensions shown in inches and (mm).

Test Circuits (Continued)

8. Channel-to-Channel Crosstalk

S

D

0.1

m

F

V

DD

V

S

GND

V

SS

50

V

NC

0.1

m

F

V

IN1

V

IN2

S

D

R

L

50

V

V

OUT

CHANNEL TO CHANNEL

CROSSTALK = 20

3

LOG V

S

/V

OUT

V

DD

V

SS

APPLIC AT ION

Figure 9 illustrates a precise, sample-and-hold circuit. An

AD845 is used as the input buffer while the output operational

amplifier is an OP07. During the track mode, SW1 is closed and

the output V

OUT

follows the input signal V

IN

. In the hold mode,

SW1 is opened and the signal is held by the hold capacitor C

H

.

Due to switch and capacitor leakage, the voltage on the hold

capacitor will decrease with time. T he ADG661/ADG662/

ADG663 minimizes this droop due to its low leakage specifica-

tions. T he droop rate is further minimized by the use of a poly-

styrene hold capacitor. T he droop rate for the circuit shown is

typically 15

μ

V/

μ

s.

A second switch SW2, which operates in parallel with SW1, is

included in this circuit to reduce pedestal error. Since both

switches will be at the same potential, they will have a differen-

tial effect on the op amp OP07 which will minimize charge

injection effects. Pedestal error is also reduced by the compensa-

tion network R

C

and C

C

. T his compensation network also re-

duces the hold time glitch while optimizing the acquisition time.

Using the illustrated op amps and component values, the pedes-

tal error has a maximum value of 5 mV over the

±

3 V input

range. T he acquisition time is 2.5 ms while the settling time is

1.85

μ

s.

+5V

–5V

2200pF

R

C

75

V

C

1000pF

C

H

2200pF

V

OUT

ADG661

ADG662

ADG663

SW2

SW1

S

S

D

D

+5V

–5V

AD845

+5V

–5V

V

IN

OP07

Figure 9. Accurate Sample-and-Hold

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADG663BRU | Tantalum Molded Capacitor; Capacitance: 33uF; Voltage: 10V; Case Size: 5.8x2.3 mm; Packaging: Tape & Reel |

| ADG701 | Low Voltage SPST Switches(低壓2Ω單刀單擲開關(guān)) |

| ADG702 | Low Voltage SPST Switches(低壓2Ω單刀單擲開關(guān)) |

| ADG702BRM | CMOS Low Voltage 2ohm SPST Switches |

| ADG701BRM | CMOS Low Voltage 2ohm SPST Switches |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADG663BRU | 制造商:Analog Devices 功能描述:Analog Switch Quad SPST 16-Pin TSSOP 制造商:Analog Devices 功能描述:SWITCH QUAD SPST SMD TSSOP16 663 |

| ADG663BRU-REEL | 制造商:Analog Devices 功能描述:Analog Switch Quad SPST 16-Pin TSSOP T/R 制造商:Analog Devices 功能描述:ANLG SW QUAD SPST 5.5V/5.5V 16TSSOP - Tape and Reel |

| ADG663BRU-REEL7 | 制造商:Analog Devices 功能描述:Analog Switch Quad SPST 16-Pin TSSOP T/R |

| ADG663BRUZ | 制造商:Analog Devices 功能描述:Analog Switch Quad SPST 16-Pin TSSOP 制造商:Analog Devices 功能描述:SWITCH QUAD SPST SMD TSSOP16 663 |

| ADG701 | 制造商:AD 制造商全稱:Analog Devices 功能描述:CMOS Low Voltage 2ohm SPST Switches |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。