- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382830 > ADC0804S040TS (NXP Semiconductors N.V.) Single 8-bit ADC up to 40 Msps PDF資料下載

參數(shù)資料

| 型號: | ADC0804S040TS |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | 外設(shè)及接口 |

| 英文描述: | Single 8-bit ADC up to 40 Msps |

| 封裝: | ADC0804S040TS/C1<SOT341-1 (SSOP28)|<<http://www.nxp.com/packages/SOT341-1.html<1<Always Pb-free,;ADC0804S040TS/C1<SOT341-1 (SSOP28)|<<http://www.nxp.com/packages/SOT341-1 |

| 文件頁數(shù): | 9/19頁 |

| 文件大小: | 133K |

| 代理商: | ADC0804S040TS |

ADC0804S030_040_050_2

NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 02 — 14 August 2008

9 of 19

NXP Semiconductors

ADC0804S030/040/050

Single 8 bits ADC, up to 30 MHz, 40 MHz or 50 MHz

[1]

In addition to a good layout of the digital and analog ground, it is recommended that the rise and fall times of the clock must not be less

than 0.5 ns.

[2]

Analog input voltages producing code 0 up to and including code 255:

a) V

offset

BOTTOM is the difference between the analog input which produces data equal to 00 and the reference voltage on pin RB

(V

RB

) at T

amb

= 25

°

C.

b) V

offset

TOP is the difference between the reference voltage on pin RT (V

RT

) and the analog input which produces data outputs equal

to code 255 at T

amb

= 25

°

C

.

To ensure the optimum linearity performance of such a converter architecture the lower and upper extremities of the converter reference

resistor ladder are connected to pins RB and RT via offset resistors R

OB

and R

OT

as shown in

Figure 3

.

V

V

–

OB

L

OT

[3]

a) The current flowing into the resistor ladder is

and the full-scale input range at the converter, to cover code 0

to 255 is

b) Since R

L

, R

OB

and R

OT

have similar behavior with respect to process and temperature variation, the ratio

will be kept reasonably constant from device to device. Consequently, the variation of the output codes at a given input voltage

depends mainly on the difference V

RT

V

RB

and its variation with temperature and supply voltage. When several ADCs are

connected in parallel and fed with the same reference source, the matching between each of them is optimized.

[4]

[5]

The analog bandwidth is defined as the maximum input sine wave frequency which can be applied to the device. No glitches greater

than 0.5 LSB, neither any significant attenuation are observed in the reconstructed signal.

[6]

The analog input settling time is the minimum time required for the input signal to be stabilized after a sharp full-scale input (square

wave signal) in order to sample the signal and obtain correct output data.

Differential phase

[9]

dif

differential phase

f

clk

= 40 MHz;

PAL modulated ramp

-

0.4

-

deg

Timing (f

clk

= 40 MHz; C

i

= 15 pF); see

Figure 4

[10]

t

d(s)

sampling delay time

t

h(o)

output hold time

t

d(o)

output delay time

-

4

-

-

-

3

-

10

12

-

-

-

13

15

15

ns

ns

ns

ns

pF

V

CCO

= 4.75 V

V

CCO

= 3.15 V

C

L

3-state output delay times; see

Figure 5

t

dZH

float to active HIGH

delay time

t

dZL

float to active LOW

delay time

t

dHZ

active HIGH to float

delay time

t

dLZ

active LOW to float

delay time

load capacitance

-

5.5

8.5

ns

-

12

15

ns

-

19

24

ns

-

12

15

ns

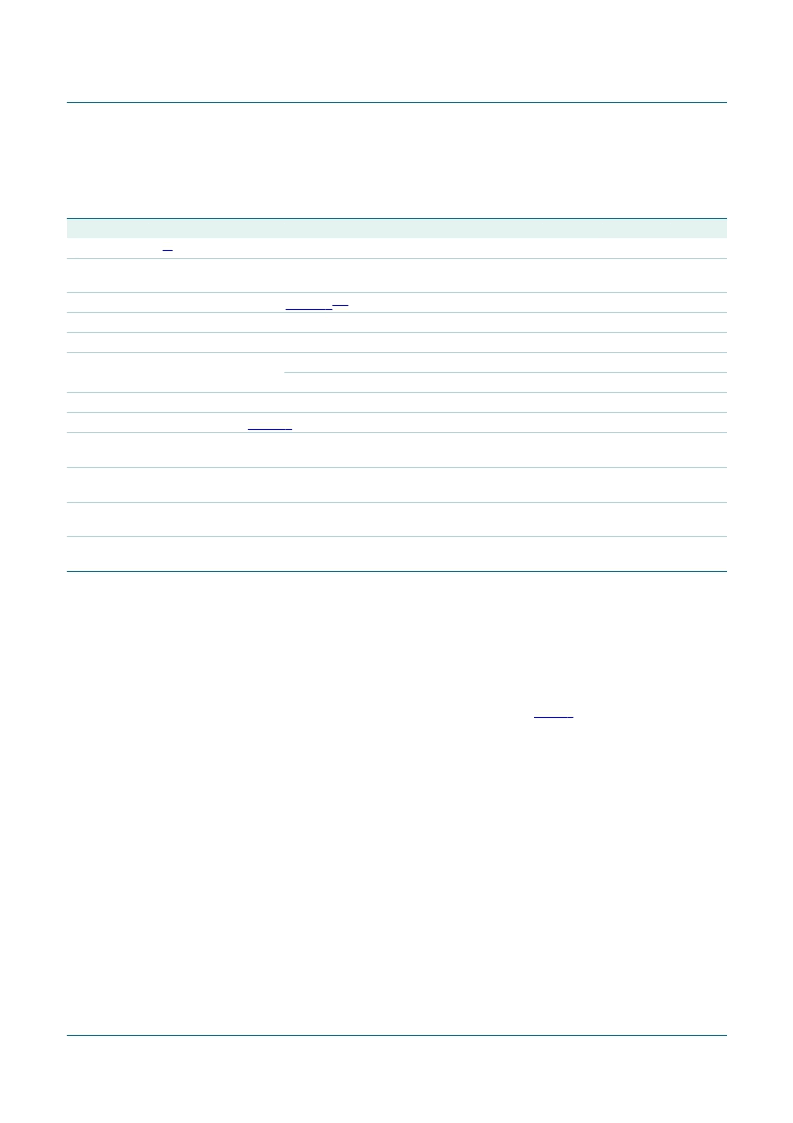

Table 6.

V

CCA

= V3 to V4 = 4.75 V to 5.25 V; V

CCD

= V11 to V12 and V28 to V27 = 4.75 V to 5.25 V;

V

CCO

= V13 to V14 = 3.0 V to 5.25 V; AGND and DGND shorted together; T

amb

= 0

°

C to 70

°

C; typical values measured at

V

CCA

= V

CCD

= 5 V and V

CCO

= 3.3 V V

i(a)(p-p)

= 2.0 V; C

L

= 15 pF and T

amb

= 25

°

C; unless otherwise specified.

Symbol

Parameter

Conditions

Characteristics

Min

Typ

Max

Unit

I

----------------------------------------

=

V

I

R

L

I

L

×

R

L

OB

OT

----------------------------------------

V

RT

V

RB

+

(

)

×

0.852

V

RT

V

RB

–

(

)

×

=

=

=

R

L

OB

OT

----------------------------------------

E

G

V

--------------------------------------------------------

V

–

i p

(

)

V

p

–

)

–

p

–

(

)

100

×

=

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADC0804S050TS | Single 8-bit ADC up to 50 Msps |

| ADC0808S125HW | Single 8-bit ADC, up to 125 Msps |

| ADC0808S125HW | Single 8-bit ADC, up to 125 Msps |

| ADC0808S250HW | Single 8-bit ADC, up to 250 Msps |

| ADC1002S020HL | Single 10 bits ADC, up to 20 MHz |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADC0804S040TS/C1'1 | 制造商:NXP Semiconductors 功能描述:ADC 8BIT PAR 40MHZ 28-SSOP |

| ADC0804S040TS/C1,1 | 功能描述:視頻模擬/數(shù)字化轉(zhuǎn)換器集成電路 SGL 8-BIT ADC 30MSPS RoHS:否 制造商:Texas Instruments 輸入信號類型:Differential 轉(zhuǎn)換器數(shù)量:1 ADC 輸入端數(shù)量:4 轉(zhuǎn)換速率:3 Gbps 分辨率:8 bit 結(jié)構(gòu): 輸入電壓:3.3 V 接口類型:SPI 信噪比: 電壓參考: 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:TCSP-48 封裝:Reel |

| ADC0804S040TS/C1,118 | 制造商:NXP Semiconductors 功能描述: |

| ADC0804S040TS/C1’1 | 功能描述:視頻模擬/數(shù)字化轉(zhuǎn)換器集成電路 ADC Single 40MSPS 8-Bit Parallel 28Pin RoHS:否 制造商:Texas Instruments 輸入信號類型:Differential 轉(zhuǎn)換器數(shù)量:1 ADC 輸入端數(shù)量:4 轉(zhuǎn)換速率:3 Gbps 分辨率:8 bit 結(jié)構(gòu): 輸入電壓:3.3 V 接口類型:SPI 信噪比: 電壓參考: 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:TCSP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。