- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375249 > AD995PCBZ (Analog Devices, Inc.) 1 GSPS Quadrature Digital Upconverter w/18-Bit IQ Data Path and 14-Bit DAC PDF資料下載

參數(shù)資料

| 型號: | AD995PCBZ |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 1 GSPS Quadrature Digital Upconverter w/18-Bit IQ Data Path and 14-Bit DAC |

| 中文描述: | 1 GSPS的正交數(shù)字上變頻器w/18-Bit智商數(shù)據(jù)路徑和14位DAC |

| 文件頁數(shù): | 16/38頁 |

| 文件大?。?/td> | 602K |

| 代理商: | AD995PCBZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁

AD9957

PRELIMINARY TECHNICAL DATA

Rev. PrF | Page 16 of 38

two outputs. The use of balanced outputs reduces the amount of

common-mode noise at the DAC output, increasing signal-to-

noise ratio. An external resistor (R

SET

) connected between the

DAC_R

SET

pin and the DAC ground (AGND_DAC) establishes

a reference current. The full-scale output current of the DAC

(I

OUT

) is produced as a scaled version of the reference current

(see the Auxiliary DAC section that follows).

Proper attention should be paid to the load termination to keep the

output voltage within the specified compliance range, as voltages

developed beyond this range will cause excessive distortion and

might even damage the DAC output circuitry.

Auxiliary DAC

The full scale output current of the main DAC (I

OUT

) is con-

trolled by an 8-bit auxiliary DAC. An 8-bit code word stored in

the appropriate register map location sets I

OUT

according to the

following equation:

+

=

96

4

86

R

CODE

I

SET

OUT

(6)

Where R

SET

is the value of the R

SET

resistor (in ohms) and CODE

is the 8-bit value supplied to the auxiliary DAC (default is 127).

For example, with R

SET

=10,000 and CODE=127, then

I

OUT

=20.07mA.

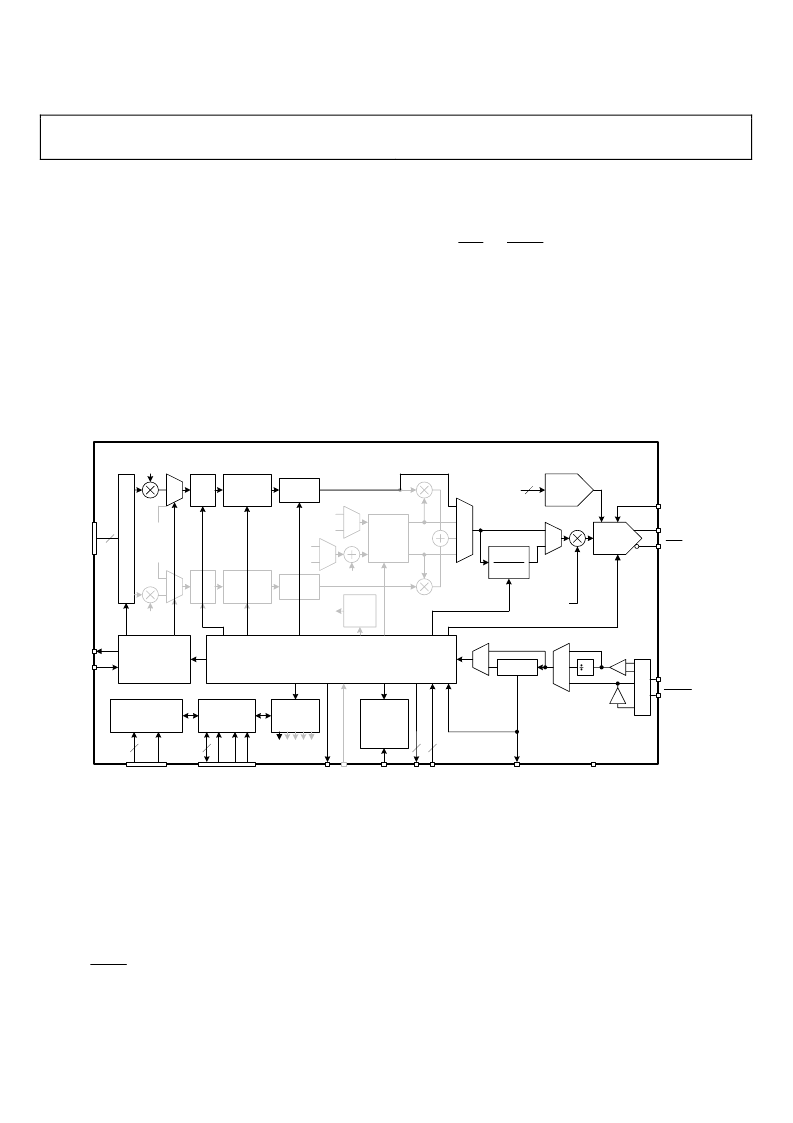

INTERPOLATING DAC MODE

A block diagram of the AD9957 operating in the interpolating

DAC mode is shown in Figure 11; grayed out items are inactive.

In this mode, the Q data path, DDS and modulator are all dis-

abled; only the I data path is active.

CCI

(1x -63x)

DDS

cos(

ω

t+

θ

)

sin(

ω

t+

θ

)

DAC

(14-b)

θ

Halfband

Filters

(4x)

18

Parallel Data

Timing &

Control

I/Q In

Internal Clock Timing & Control

PDClk

Clock

Multiplier

RefClk

P

RefClk

Halfband

Filters

(4x)

Inv.

CCI

Inv.

CCI

DAC

Rset

Iout

Iout

1

0

1

D

R

0

1

AD9957: Interpolating DAC Mode

0

3

2

1

0

1

x

sin(x)

TxEn

ω

2

0

1

2

C

OSF

AUX

DAC

(8-b)

8

DAC

Gain

Serial I/O

Port

S

S

Programming

Registers

2

S

P

3

R

RAM

Power

Down

Control

P

D

C

I

Q

C

S

θ

F

2

S

2

G

O

FTW

θ

0

1

Freq.

Ramp

Logic

PW

F

0

1

R

R

CCI

(1x -63x)

Q

I

I

Figure 11: Interpolating DAC Mode

As in the quadrature modulation mode, the PDCLK pin func-

tions as a clock which serves to synchronize the input of data to

the AD9957. The PDCLK rate is given below. Note that it oper-

ates at a rate that is half of that for the quadrature modulation

mode.

R

f

f

SYSCLK

4

DATA

=

(Interpolating DAC mode)

Because no modulation takes place, the spectrum of the data

supplied at the parallel port remains at base band. However, a

sample rate conversion takes place based on the programmed

interpolation rate. The interpolation hardware processes the

signal, by effectively performing an over-sample with zero-

stuffing operation. However, the original input spectrum re-

mains intact and the images that would otherwise occur from

the sample rate conversion process are suppressed by the inter-

polation signal chain.

The PDCLK pin is an output and serves as a data clock timing

source. The output clock rate is f

DATA

as explained in the

Input

Data Assembler

section. Each PDCLK rising edge latches a data

word into the I data path.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9959 | 4 Channel 500MSPS DDS with 10-bit DACs |

| AD9979 | 14-Bit, CCD Signal Processor with Precision Timing Core |

| AD9980 | High Performance 8-Bit Display Interface |

| AD9980KSTZ-80 | High Performance 8-Bit Display Interface |

| AD9980KSTZ-95 | High Performance 8-Bit Display Interface |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9960BSTZ | 功能描述:RFID應(yīng)答器 MxFE for RFID Reader Transceiver RoHS:否 制造商:Murata 存儲(chǔ)容量:512 bit 工作溫度范圍:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體: 封裝:Reel |

| AD9960BSTZRL | 功能描述:IC MXFE FOR RFID READER/TXRX RoHS:是 類別:RF/IF 和 RFID >> RFID IC 系列:AD9960B 其它有關(guān)文件:CR14 View All Specifications 標(biāo)準(zhǔn)包裝:1 系列:- RF 型:收發(fā)器 頻率:13.56MHz 特點(diǎn):ISO14443-B 封裝/外殼:16-SOIC(0.154",3.90mm 寬) 供應(yīng)商設(shè)備封裝:16-SO 包裝:Digi-Reel® 其它名稱:497-5719-6 |

| AD9960XSTZ | 制造商:Analog Devices 功能描述:SINGLE-SUPPLY CABLE MODEM/SET-TOP BOX MIXED-SIGNAL FRONT END - Trays |

| AD9961 | 制造商:AD 制造商全稱:Analog Devices 功能描述:10-/12-Bit, Low Power, Broadband MxFE |

| AD9961_12 | 制造商:AD 制造商全稱:Analog Devices 功能描述:10-/12-Bit, Low Power, Broadband MxFE |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。