- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373969 > AD9870 (ANALOG DEVICES INC) IF Digitizing Subsystem PDF資料下載

參數(shù)資料

| 型號: | AD9870 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | IF Digitizing Subsystem |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP48 |

| 封裝: | 1.40 MM HEIGHT, PLASTIC, TQFP-48 |

| 文件頁數(shù): | 5/20頁 |

| 文件大小: | 233K |

| 代理商: | AD9870 |

REV. 0

AD9870

–5–

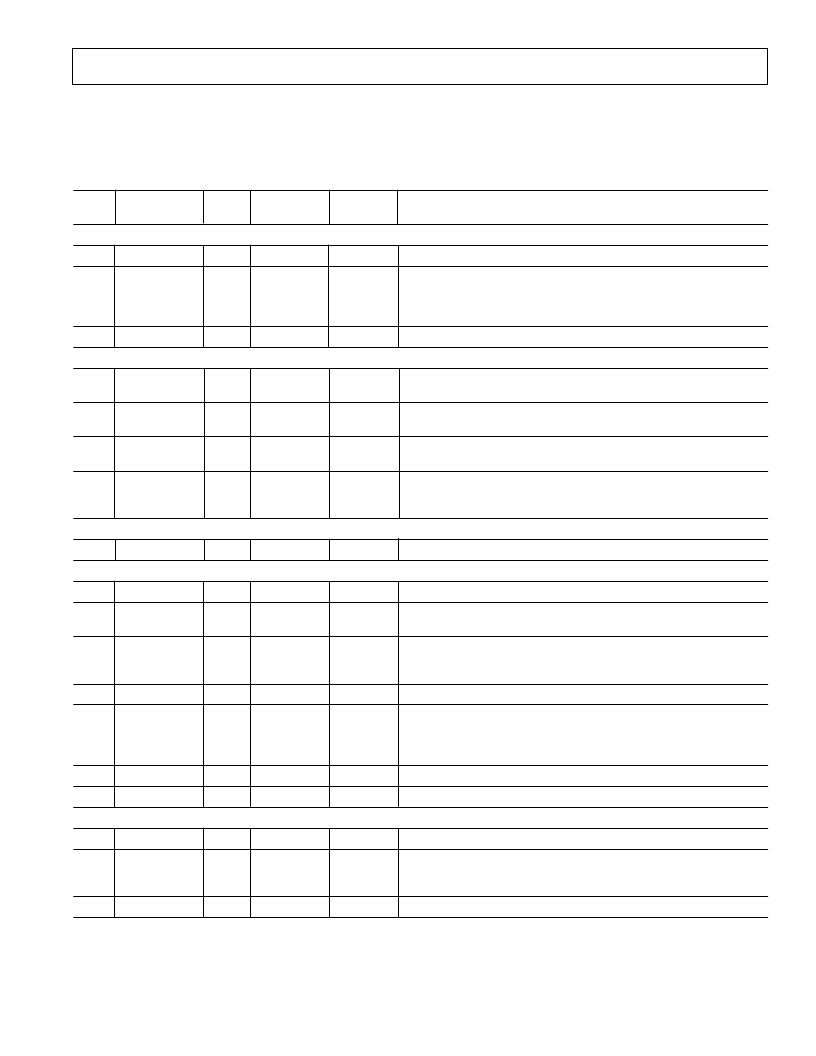

SERIAL PERIPHERAL INTERFACE (SPI)

The Serial Peripheral Interface (SPI) is a bidirectional serial port. It is used to load configuration information into the registers listed

below as well as to read back their contents. Table I provides a list of the registers that may be programmed through the SPI port.

Addresses and default values are given in hexadecimal form.

Table I. SPI Address Map

Address Bit

(Hex)

Breakdown

Width

Default Value

Name

Description

POWER CONTROL REGISTERS

0x00

(7:0)

8

0xFF

STBY

Standby Control Bits (REF, LO, CKO, CK, GC, LNAMX, VGA, ADC).

0x01

(7:6)

(5:4)

(3:2)

(1:0)

2

2

2

2

0

0

0

1

LNAB

MIXB

CKOB

ADCB

LNA Bias Current (0 = 0.5 mA, 1 = 1 mA, 2 = 2 mA, 3 = 3 mA).

Mixer Bias Current (0 = 1 mA, 1 = 2 mA, 2 = 3 mA, 3 = 4 mA).

CK Oscillator Bias (0 = 0.25 mA, 1 = 0.35 mA, 2 = 0.53 mA, 3 = 0.85 mA).

ADC Amplifier Bias (0 = 2.4 mA, 1 = 3.2 mA, 2 = 4.0 mA, 3 = 4.8 mA).

0x02

(7:0)

8

0x00

TEST

Factory Test Mode.

AGC

0x03

(7)

(6:0)

1

7

0

0x3F

ATTEN

AGCG(14:8) AGC Gain Setting (7 MSBs of a 15-bit two’s-complement word).

Apply 16 dB attenuation in the front end.

0x04

(7:0)

8

0xFF

AGCG(7:0)

AGC Gain Setting (8 LSBs of a 15-bit two’s-complement word).

Default corresponds to maximum gain.

0x05

(7:4)

(3:0)

4

4

0

0

AGCA

AGCD

AGC Attack Time Setting. Default yields 50 Hz raw loop bandwidth.

AGC Decay Time Setting. Default is decay time = attack time.

0x06

(7:4)

(3:0)

(2:0)

4

4

3

0

0

0

AGCO

AGCD

AGCR

AGC Overload Update Setting. Default is slowest update.

Fast AGC (Minimizes resistance seen between GCN and GCP).

AGC Enable/Reference Level (disabled, 3 dB, 6 dB, 9 dB, 12 dB, 15 dB below clip).

DECIMATION FACTOR

0x07

(3:0)

4

4

M

Decimation Factor = 60

×

(M + 1). Default is decimate-by-300.

LO SYNTHESIZER

0x08

(5:0)

6

0x00

LOR(13:8)

Reference Frequency Divisor (6 MSBs of a 14-Bit Word).

0x09

(7:0)

8

0x38

LOR(7:0)

Reference Frequency Divisor (8 LSBs of a 14-Bit Word).

Default (56) Yields 300 kHz from f

REF

= 16.8 MHz.

0x0A

(7:5)

(4:0)

3

5

0x5

0x00

LOA

LOB(12:8)

“A” Counter (Prescaler Control Counter).

“B” Counter MSBs (5 MSBs of a 13-Bit Word).

Default LOA and LOB Values Yield 300 kHz from 73.35 MHz–2.25 MHz.

0x0B

(7:0)

8

0x1D

LOB(7:0)

“B” Counter LSBs (8 LSBs of a 13-Bit Word).

0x0C

(6)

(5)

(4:2)

(1:0)

1

1

3

2

0

0

0

0

LOF

LOINV

LOI

LOTM

Enable Fast Acquire.

Invert Charge Pump (0 = Pump_Up

IOUTL Sources Current).

Charge Pump Current in Normal Operation. I

PUMP

= (LOI + 1)

×

0.625 mA.

Manual Control of LO Charge Pump (3 = Off, 2 = Down, 1 = Up, 0 = Normal).

0x0D

(3:0)

4

0x0

LOFA(13:8)

LO Fast Acquire Time Unit (4 MSBs of a 14-Bit Word).

0x0E

(7:0)

8

0x04

LOFA(7:0)

LO Fast Acquire Time Unit (8 LSBs of a 14-Bit Word).

CLOCK SYNTHESIZER

0x10

(5:0)

6

00

CKR(13:8)

Reference Frequency Divisor (6 MSBs of a 14-Bit Word).

0x11

(7:0)

8

0x38

CKR(7:0)

Reference Frequency Divisor (8 LSBs of a 14-Bit Word).

Default Yields 300 kHz from f

REF

=16.8 MHz.

Min = 3, Max = 16383.

0x12

(4:0)

5

0x00

CKN(12:8)

Synthesized Frequency Divisor (5 MSBs of a 13-Bit Word).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9870EB | IF Digitizing Subsystem |

| AD9873 | Analog Front End Converter for Set-Top Box, Cable Modem |

| AD9873-EB | Analog Front End Converter for Set-Top Box, Cable Modem |

| AD9873JS | Analog Front End Converter for Set-Top Box, Cable Modem |

| AD9874 | IF Digitizing Subsystem |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9870AST | 制造商:Rochester Electronics LLC 功能描述:GENERAL PURPOSE IF SUBSYSTEM - Tape and Reel 制造商:Analog Devices 功能描述: |

| AD9870EB | 制造商:AD 制造商全稱:Analog Devices 功能描述:IF Digitizing Subsystem |

| AD9873 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Analog Front End Converter for Set-Top Box, Cable Modem |

| AD9873-EB | 制造商:Analog Devices 功能描述: |

| AD9873JS | 制造商:Analog Devices 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。