- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄165343 > AD9643BCPZ-170 (ANALOG DEVICES INC) 2-CH 14-BIT FLASH METHOD ADC, PARALLEL ACCESS, QCC64 PDF資料下載

參數(shù)資料

| 型號: | AD9643BCPZ-170 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 2-CH 14-BIT FLASH METHOD ADC, PARALLEL ACCESS, QCC64 |

| 封裝: | 9 X 9 MM, ROHS COMPLIANT, MO-220VMMD-4, LFCSP-64 |

| 文件頁數(shù): | 28/36頁 |

| 文件大?。?/td> | 1659K |

| 代理商: | AD9643BCPZ-170 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當(dāng)前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

AD9643

Rev. A | Page 34 of 36

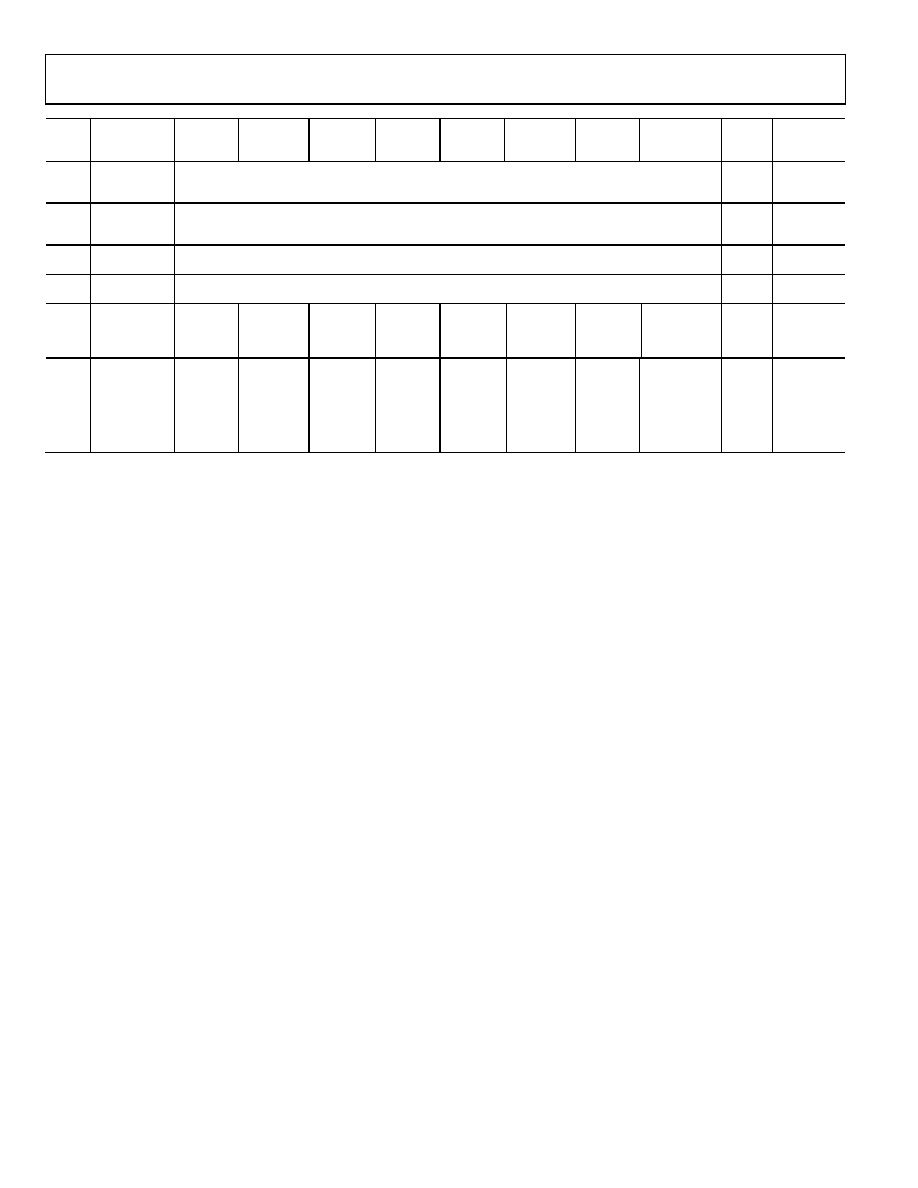

Addr

(Hex)

Register

Name

Bit 7

(MSB)

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

(LSB)

Default

Value

(Hex)

Default

Notes/

Comments

0x1F

User Test

Pattern 4 LSB

(global)

User Test Pattern 4[7:0]

0x00

0x20

User Test

Pattern 4 MSB

(global)

User Test Pattern 4[15:8]

0x00

0x24

BIST signature

LSB (local)

BIST signature[7:0]

0x00

Read only.

0x25

BIST signature

MSB (local)

BIST signature[15:8]

0x00

Read only.

0x3A

Sync control

(global)

Open

Clock

divider

next sync

only

Clock

divider

sync

enable

Master sync

buffer enable

0x00

0x59

SYNC pin

control

(local)

Open

SYNC pin

sensitivity

0 = sync

on high

level

1 = sync

on edge

SYNC pin

edge

sensitivity

0 = sync on

falling edge

1 = sync on

rising edge

0x00

1 The channel index register at Address 0x05 should be set to 0x03 (default) when writing to Address 0x00.

MEMORY MAP REGISTER DESCRIPTION

For more information on functions controlled in Register 0x00

to Register 0x25, see the AN-877 Application Note, Interfacing

to High Speed ADCs via SPI.

Sync Control (Register 0x3A)

Bits[7:3]—Reserved

Bit 2—Clock Divider Next Sync Only

If the master sync buffer enable bit (Address 0x3A, Bit 0) and

the clock divider sync enable bit (Address 0x3A, Bit 1) are high,

Bit 2 allows the clock divider to sync to the first sync pulse that

it receives and to ignore the rest. The clock divider sync enable

bit (Address 0x3A, Bit 1) resets after it syncs.

Bit 1—Clock Divider Sync Enable

Bit 1 gates the sync pulse to the clock divider. The sync signal is

enabled when Bit 1 is high and Bit 0 is high. This is continuous

sync mode.

Bit 0—Master Sync Buffer Enable

Bit 0 must be set high to enable any of the sync functions. If the

sync capability is not used, this bit should remain low to

conserve power.

SYNC Pin Control (Register 0x59)

Bits [7:2]—Reserved

Bit 1—SYNC Pin Sensitivity

If Bit 1 is set to 0, the SYNC input responds to a level. If this bit

is set low, the SYNC input responds to the edge (rising or

falling) set in Bit 0 of Address 0x59.

Bit 0—SYNC Pin Edge Sensitivity

If Bit 1 is set high, setting Bit 0 to a 0 causes the SYNC input to

respond to a falling edge. If this bit is set, the SYNC input

respond to a rising edge.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9643BCPZ-210 | 2-CH 14-BIT FLASH METHOD ADC, PARALLEL ACCESS, QCC64 |

| AD9643BCPZ-250 | 2-CH 14-BIT FLASH METHOD ADC, PARALLEL ACCESS, QCC64 |

| AD9643BCPZRL7-210 | 2-CH 14-BIT FLASH METHOD ADC, PARALLEL ACCESS, QCC64 |

| AD9753ASTZRL | PARALLEL, WORD INPUT LOADING, 0.011 us SETTLING TIME, 12-BIT DAC, PQFP48 |

| ADA123AL7 | FIBER OPTIC ADD/DROP MUX/DEMUX, LC/UPC CONNECTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9643BCPZ-210 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 14 Bit 210Msps Dual ADC RoHS:否 制造商:Analog Devices 通道數(shù)量: 結(jié)構(gòu): 轉(zhuǎn)換速率: 分辨率: 輸入類型: 信噪比: 接口類型: 工作電源電壓: 最大工作溫度: 安裝風(fēng)格: 封裝 / 箱體: |

| AD9643BCPZ-250 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 14 Bit 250Msps Dual ADC RoHS:否 制造商:Analog Devices 通道數(shù)量: 結(jié)構(gòu): 轉(zhuǎn)換速率: 分辨率: 輸入類型: 信噪比: 接口類型: 工作電源電壓: 最大工作溫度: 安裝風(fēng)格: 封裝 / 箱體: |

| AD9643BCPZRL7-170 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 14 Bit 170Msps Dual ADC RoHS:否 制造商:Analog Devices 通道數(shù)量: 結(jié)構(gòu): 轉(zhuǎn)換速率: 分辨率: 輸入類型: 信噪比: 接口類型: 工作電源電壓: 最大工作溫度: 安裝風(fēng)格: 封裝 / 箱體: |

| AD9643BCPZRL7-210 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 14 Bit 210Msps Dual ADC RoHS:否 制造商:Analog Devices 通道數(shù)量: 結(jié)構(gòu): 轉(zhuǎn)換速率: 分辨率: 輸入類型: 信噪比: 接口類型: 工作電源電壓: 最大工作溫度: 安裝風(fēng)格: 封裝 / 箱體: |

| AD9643BCPZRL7-250 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 14 Bit 250Msps Dual ADC RoHS:否 制造商:Analog Devices 通道數(shù)量: 結(jié)構(gòu): 轉(zhuǎn)換速率: 分辨率: 輸入類型: 信噪比: 接口類型: 工作電源電壓: 最大工作溫度: 安裝風(fēng)格: 封裝 / 箱體: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。