- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375235 > AD6650PCB (Analog Devices, Inc.) Diversity IF to Baseband GSM/EDGE Narrowband Receiver PDF資料下載

參數(shù)資料

| 型號(hào): | AD6650PCB |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Diversity IF to Baseband GSM/EDGE Narrowband Receiver |

| 中文描述: | 多樣性IF到基帶的GSM / EDGE窄帶接收器 |

| 文件頁(yè)數(shù): | 22/28頁(yè) |

| 文件大小: | 594K |

| 代理商: | AD6650PCB |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)

Preliminary Technical Data

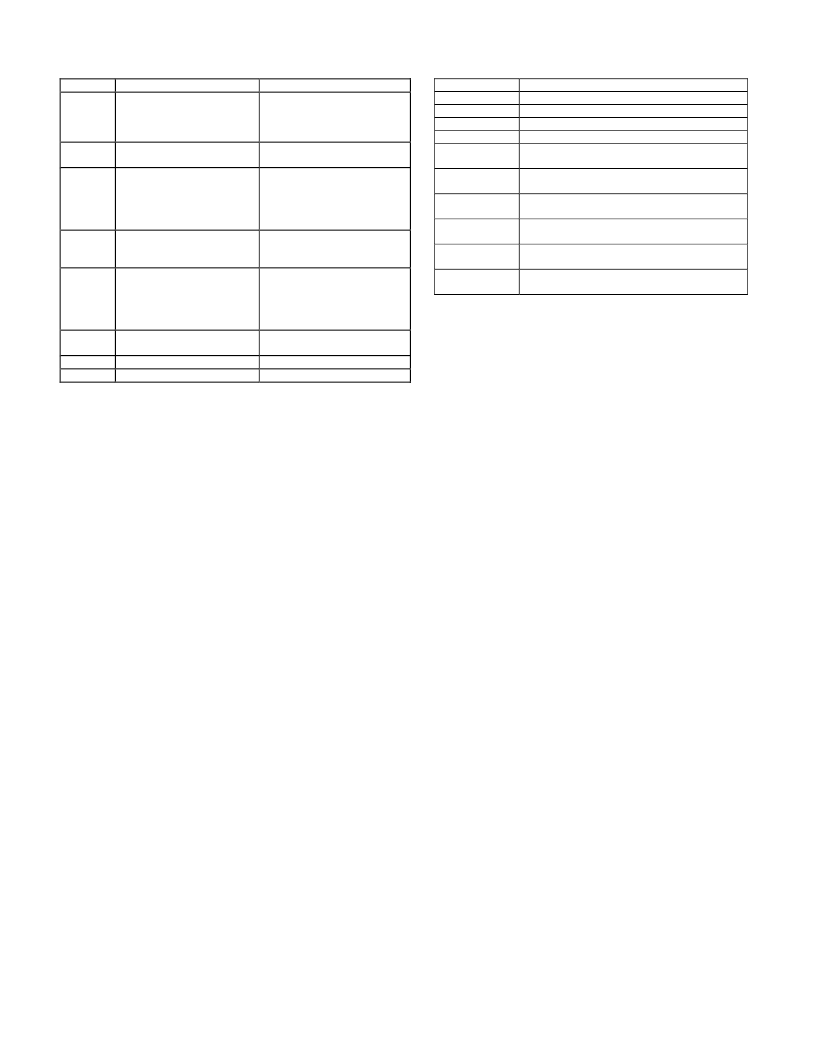

External Memory Map

A[2:0]

Name

Comment

111

Access Control Register

(ACR)

6: Broadcast

5-2: Instruction[3:0]

1-0: A[9:8]

110

Channel Address Register

(CAR)

101

Special Function Register 2

(SF2)

5: DC correction sync enable

4: PN sync enable

3-1: Reserved

0: Issue soft sync

100

Special Function Register 1

(SF1)

4: Enable edge-sensitivity

3-1: Reserved

011

Special Function Register 0

(SF0)

3: Status of Channel B

2: Enable Channel B

1: Status of Channel A

0: Enable Channel A

010

Data Register 2 (DR2)

7-4: Reserved

3-0: D[19:16]

001

Data Register 1 (DR1)

15-8: D[15:8]

000

Data Register 0 (DR0)

7-0: D[7:0]

Table xx. External Memory Map

AD6650

REV. PrJ 02/27/2003

22

7: Auto Increment

7-0: A[7:0]

6: AGC sync Enable

5: First Sync only

7-4: Reserved

Access Control Register (ACR)

The Access Control Register serves to define the channel or

channels that receive an access from the micro-port or I

2

C

port.

Bit 7 of this register is the Auto-Increment bit. If this bit is a

1 then the CAR register described below will increment its

value after every access to the channel. This allows blocks

of address space such as Coefficient Memory to be

initialized more efficiently.

Bit 6 of the register is the Broadcast bit and determines how bits

5-2 are interpreted. The Broadcast bit should be set high so that

bits 5-2, which are referred to as Instruction bits (Instruction

[3:0]), allows a single or multiple (up to 4) AD6650 chip(s) to be

configured simultaneously There are 10 possible instructions

that are defined in the table below. The x’s in the table represent

don’t cares in the digital decoding.

Microport Instructions

Instruction

0000

0001

0010

0100

1000

Comment:

All Chips will get the access.

All Chips will get the access.

All Chips will get the access.

All Chips will get the access.

All Chips with Chip_ID[0] =xxx 0 will get the

access.

All Chips with Chip_ID[0] = xxx1 will get the

access.

All Chips with Chip_ID[1:0] = xx00 will get the

access.

All Chips with Chip_ID[1:0] = xx01 will get the

access.

All Chips with Chip_ID[1:0] = xx10 will get the

access.

All Chips with Chip_ID[1:0] = xx11 will get the

access.

1

A[9:8] bits control which channel is decoded for the access.

Table xx. Microport Instructions

When broadcast is enabled (bit 6 set high) read back is not

valid because of the potential for internal bus contention.

Therefore, if read back is subsequently desired, the

broadcast bit should be set low.

Bits 1-0 of this register are address bits that decode which of

the two channels are being accessed. Because the channels

of the AD6650 cannot be programmed independently, these

bits should be set to 0.

1001

1100

1101

1110

1111

Channel Address Register (CAR)

This register represents the 8-bit internal address of each

channel. If the Auto-Increment bit of the ACR is 1 then this

value will be incremented after every access to the DR0

register, which will in turn access the location pointed to by

this address. The Channel Address register cannot be read

back while the Broadcast bit is set high.

Special Function Registers

The AD6650 has three special function registers, SF0, SF1,

and SF2 that control synchronizing and enabling the

channels. SF0 is the channel enable register, SF1 is the pin-

sync register, and SF2 is the soft-sync register. For SF0, bits

0 and 2 allow the channels A and B, respectively to come

out of sleep based on the method selected in SF1.Bits 1 and

3 are read-only and indicate whether or not channels A and

B, respectively are active. A 1 indicates the channel is active

and a 0 indicates it is not active. Bits 4 through 7 are

unused.

For SF1, if bit 0 is set to 1,then both channels will wait for a

pulse to appear on the SYNC pin before coming out of sleep;

otherwise, the channels will assume a soft start is desired

and wait for the start hold-off counter to issue a sync. When

bit 5 is set, both channels ignore all subsequent attempts to

resync once they are awake.

For SF2, bit 0 tells the startup block to run the start hold-off

counter from the value programmed into the start hold-off

counter control register and issue a sync when done. Bits 4-

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD6650BBC1 | Diversity IF to Baseband GSM/EDGE Narrowband Receiver |

| AD6652 | 12-Bit, 65 MSPS IF to Baseband Diversity Receiver |

| AD6652BBC | 12-Bit, 65 MSPS IF to Baseband Diversity Receiver |

| AD6652BC | 12-Bit, 65 MSPS IF to Baseband Diversity Receiver |

| AD6652PCB | 12-Bit, 65 MSPS IF to Baseband Diversity Receiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD6652 | 制造商:AD 制造商全稱:Analog Devices 功能描述:12-Bit, 65 MSPS IF to Baseband Diversity Receiver |

| AD6652BBC | 制造商:Analog Devices 功能描述:IF to Baseband Diversity Receiver 256-Pin CSP-BGA 制造商:Analog Devices 功能描述:IC IF TO BASEBAND RCVR SMD 6652 |

| AD6652BBCZ | 功能描述:IC IF TO BASEBAND RCVR 256CSPBGA RoHS:是 類別:RF/IF 和 RFID >> RF 其它 IC 和模塊 系列:- 標(biāo)準(zhǔn)包裝:100 系列:* |

| AD6652BC | 制造商:AD 制造商全稱:Analog Devices 功能描述:12-Bit, 65 MSPS IF to Baseband Diversity Receiver |

| AD6652BC/PCB | 制造商:Analog Devices 功能描述:Evaluation Board With AD6652 And Software |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。