- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1890 > AD5293BRUZ-50-RL7 (Analog Devices Inc)IC DGTL POT 1024POS 50K 14TSSOP PDF資料下載

參數(shù)資料

| 型號: | AD5293BRUZ-50-RL7 |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 2/24頁 |

| 文件大小: | 0K |

| 描述: | IC DGTL POT 1024POS 50K 14TSSOP |

| 標(biāo)準(zhǔn)包裝: | 1,000 |

| 接片: | 1024 |

| 電阻(歐姆): | 50k |

| 電路數(shù): | 1 |

| 溫度系數(shù): | 標(biāo)準(zhǔn)值 35 ppm/°C |

| 存儲器類型: | 易失 |

| 接口: | 4 線串行 |

| 電源電壓: | 9 V ~ 33 V,±9 V ~ 16.5 V |

| 工作溫度: | -40°C ~ 105°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 14-TSSOP(0.173",4.40mm 寬) |

| 供應(yīng)商設(shè)備封裝: | 14-TSSOP |

| 包裝: | 帶卷 (TR) |

AD5293

Rev. D | Page 10 of 24

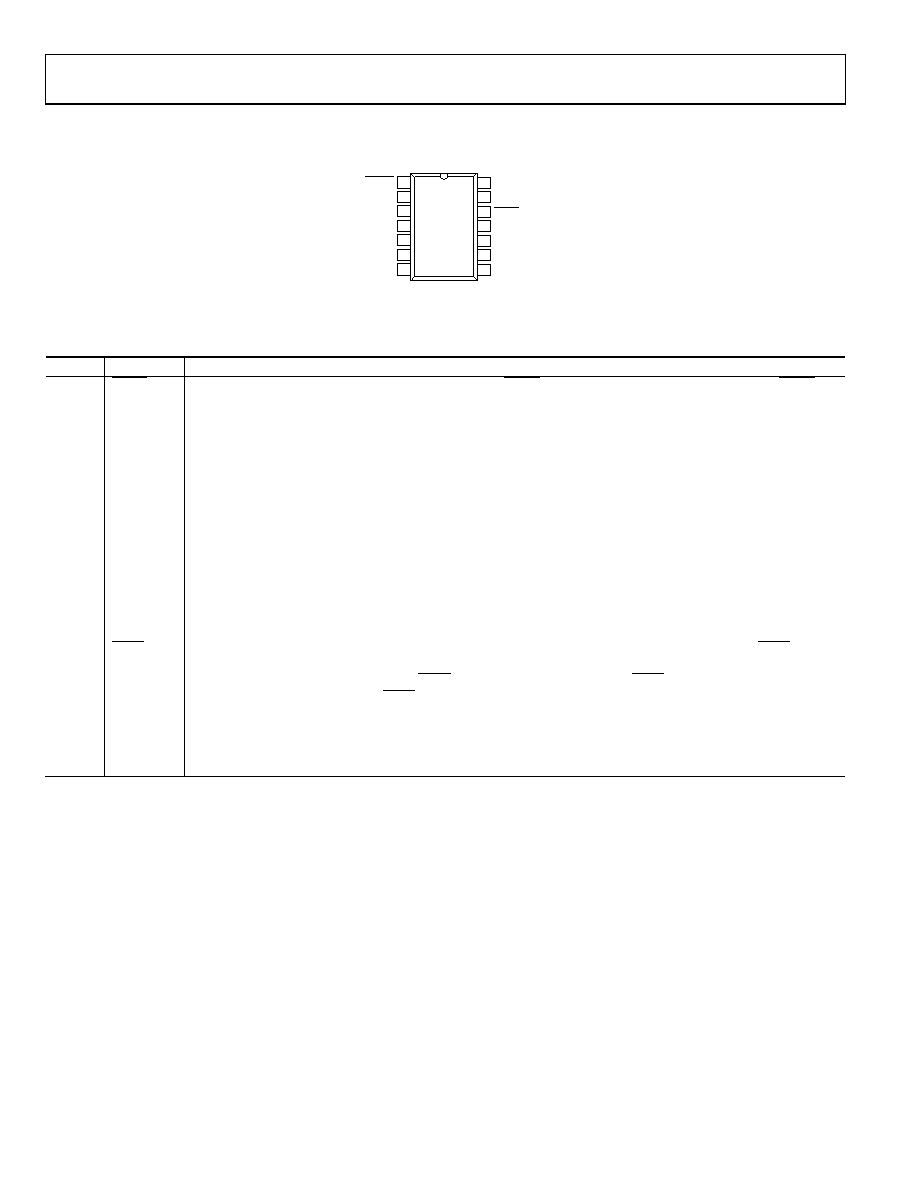

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

RESET

VSS

A

W

RDY

SYNC

VLOGIC

SCLK

B

VDD

EXT_CAP

1

2

3

4

5

6

7

DIN

GND

14

13

12

11

10

9

8

AD5293

TOP VIEW

Not to Scale

SDO

0

76

75-

0

05

Figure 5. Pin Configuration

Table 8. Pin Function Descriptions

Pin No.

Mnemonic

Description

1

RESET

Hardware Reset Pin. Sets the RDAC register to midscale. RESET is activated at the logic high transition. Tie RESET to

VLOGIC if not used.

2

VSS

Negative Supply. Connect to 0 V for single-supply applications. This pin should be decoupled with 0.1 μF ceramic

capacitors and 10 μF capacitors.

3

A

Terminal A of RDAC. VSS ≤ VA ≤ VDD.

4

W

Wiper Terminal W of RDAC. VSS ≤ VW ≤ VDD.

5

B

Terminal B of RDAC. VSS ≤ VB ≤ VDD.

6

VDD

Positive Power Supply. This pin should be decoupled with 0.1 μF ceramic capacitors and 10 μF capacitors.

7

EXT_CAP

Connect a 1 μF capacitor to EXT_CAP. This capacitor must have a voltage rating of ≥7 V.

8

VLOGIC

Logic Power Supply, 2.7 V to 5.5 V. This pin should be decoupled with 0.1 μF ceramic capacitors and 10 μF capacitors.

9

GND

Ground Pin, Logic Ground Reference.

10

DIN

Serial Data Input. This part has a 16-bit shift register. Data is clocked into the register on the falling edge of the

serial clock input.

11

SCLK

Serial Clock Input. Data is clocked into the shift register on the falling edge of the serial clock input. Data can be

transferred at rates up to 50 MHz.

12

SYNC

Falling Edge Synchronization Signal. This is the frame synchronization signal for the input data. When SYNC goes

low, it enables the shift register, and data is transferred in on the falling edges of the following clocks. The selected

register is updated on the rising edge of SYNC, following the 16th clock cycle. If SYNC is taken high before the

16th clock cycle, the rising edge of SYNC acts as an interrupt, and the write sequence is ignored by the DAC.

13

SDO

Serial Data Output. This open-drain output requires an external pull-up resistor. SDO can be used to clock data

from the serial register in daisy-chain mode or in readback mode.

14

RDY

Ready Pin. This active-high, open-drain output identifies the completion of a write or read operation to or from

the RDAC register.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD5320BRM | IC DAC 12BIT 2.7V R-R OUT 8-MSOP |

| AD5321BRM | IC DAC 12BIT 2.5V 2-WIRE 8-MSOP |

| AD5322BRM | IC DAC 12BIT DUAL R-R OUT 10MSOP |

| AD5323BRU | IC DAC 12 BIT DUAL R-R 16-TSSOP |

| AD5324BRM | IC DAC 12BIT QUAD 2.5V 10-MSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD-52PL-711A/E | 制造商:ICE TECHNOLOGY 功能描述:IC SPECIFIC ADAPTER, 52-PLCC TO 40-DIP, Convert From:52-PLCC, Convert To:40-DIP, |

| AD52YBD | 制造商:n/a 功能描述:_ |

| AD53/009-9 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD53/015-0 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD53/016-0REEL | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。